ktx2222

Member level 5

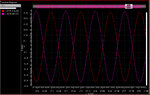

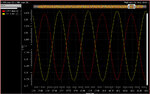

Not particularly the caps. But a RF port common mode signal will be translated to an output common mode signal, just think. So my latest question was if your balun might be unsuitable by a exposing a high common output impedance and thus promoting feedthrough of the 2nd LO harmonic generated by MN0-MN3 non-linearity.

To rate the measured voltage levels, it would be interesting to know the output "transformer" self- and mutual inductance.

So stupid I am, I cannot fully understand what you said. However, I just use ideal balun (cadence RF library).

- - - Updated - - -

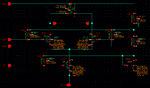

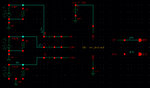

In the design of mixer u should become sure that:

1) RF transistor works in sat.

2) In half cycle one of LO transistors is off and the other one is on and other half wise versa.

3) While two LO transistors are on (middle of 2 cycles) they should be forced to work in saturation until the moment when one of them turns on and other one turns off.

All the transistors work in saturation region. I also tried to increase the VDD to enlarge the Vds margin of transistors. The problem still happens.

Do you understand clock feedthrough ?

So, the problem may be 10nF caps?? In the tutorial, 10nF caps were used. How much the block caps value I should use?