shaiko

Advanced Member level 5

Code:

process ( not_a_clock_signal ) is

begin

if rising_edge (not_a_clock_signal) then

Q <= D ;

end if ;

end process ;

process ( enable ) is

begin

if enable = '1' then

Q <= D ;

end if ;

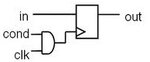

end process ;The first process describes a DFF with a gated clock while the second process describes a transparent D latch.

Am I correct ?