satiz

Member level 5

Hi there,

I doing 555 astable simulations in LT spice and I got the output. my problem is expected Ton and Toff time is not matching with my simulation results.

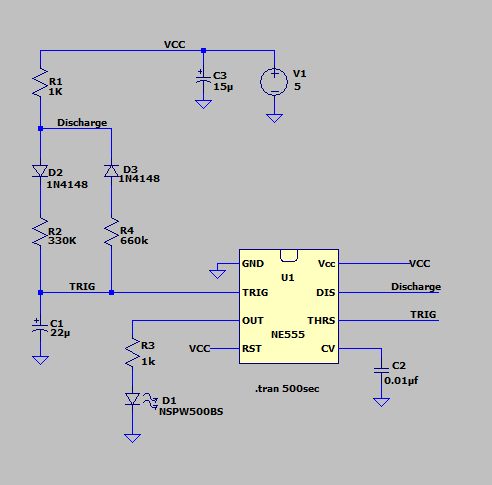

Below is my schematic.

The formula I used to calculate Ton and Toff times are given below with results:

Ton=0.693(R1+R2 x C)=5.04Sec

Toff=0.693(R4 x C)=10.06

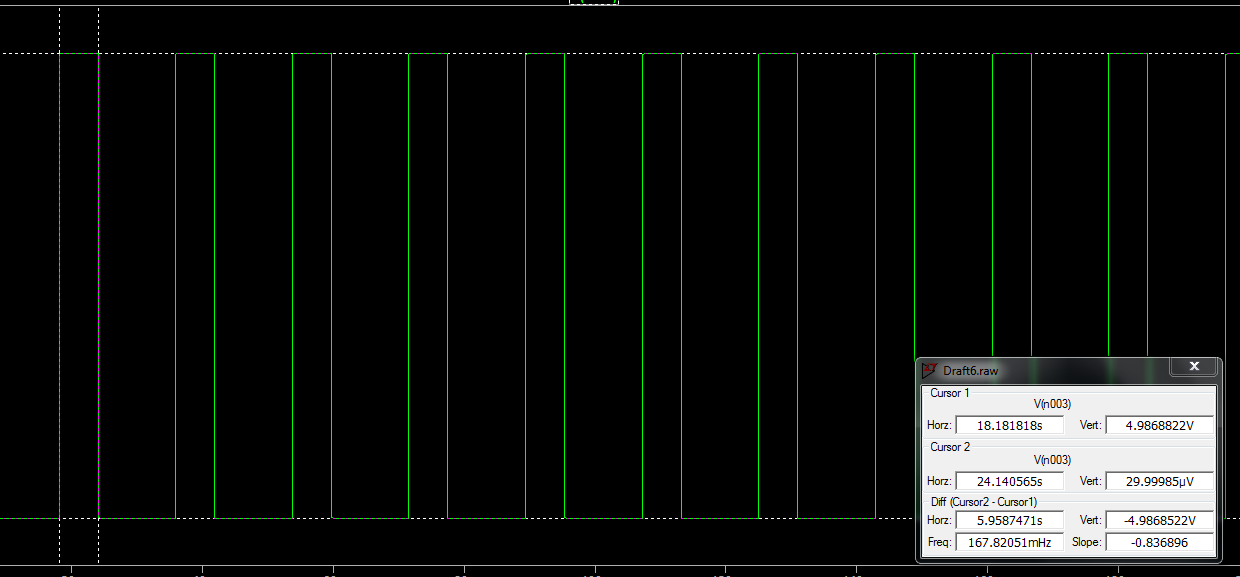

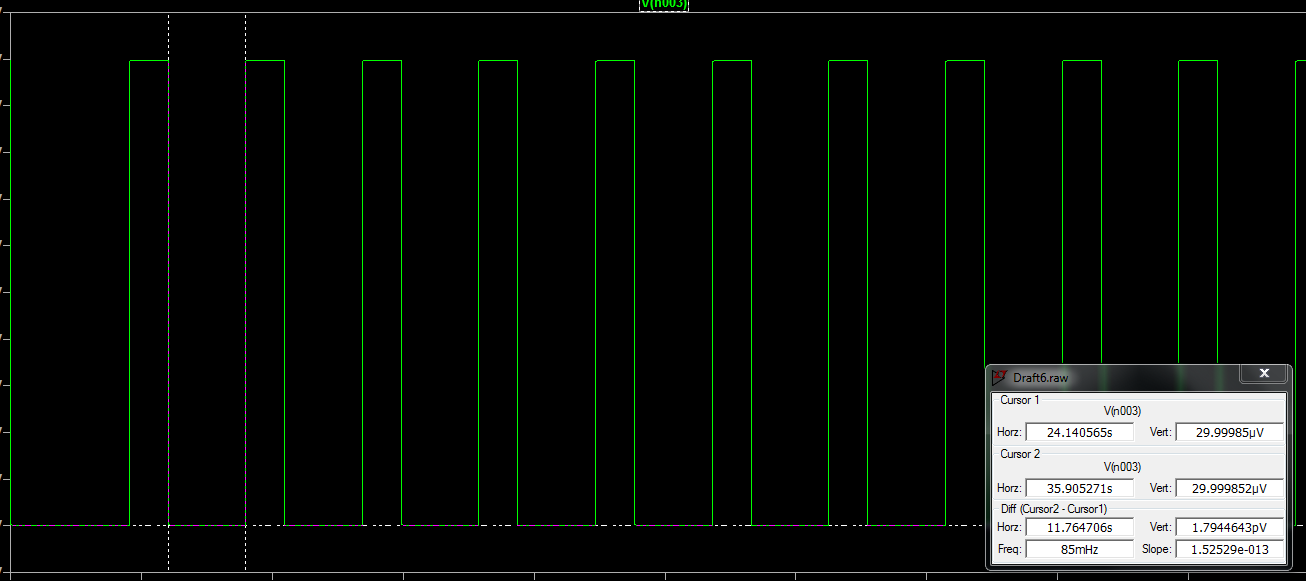

Simulation results:

Ton = 5.96Sec

Toff = 11.88 sec

I am thinking this difference is because of the D2, D3 diodes. If yes, how to include this in the formula? Please help me.

I am attaching the .asc code for reference.

I doing 555 astable simulations in LT spice and I got the output. my problem is expected Ton and Toff time is not matching with my simulation results.

Below is my schematic.

The formula I used to calculate Ton and Toff times are given below with results:

Ton=0.693(R1+R2 x C)=5.04Sec

Toff=0.693(R4 x C)=10.06

Simulation results:

Ton = 5.96Sec

Toff = 11.88 sec

I am thinking this difference is because of the D2, D3 diodes. If yes, how to include this in the formula? Please help me.

I am attaching the .asc code for reference.

Code:

Version 4

SHEET 1 1584 680

WIRE -16 -384 -320 -384

WIRE 48 -384 -16 -384

WIRE 208 -384 48 -384

WIRE -320 -352 -320 -384

WIRE 48 -352 48 -384

WIRE 208 -352 208 -384

WIRE 48 -272 48 -288

WIRE 208 -240 208 -272

WIRE -320 -208 -320 -272

WIRE -224 -208 -320 -208

WIRE -160 -208 -224 -208

WIRE -320 -144 -320 -208

WIRE -160 -144 -160 -208

WIRE -320 -16 -320 -80

WIRE -160 -16 -160 -80

WIRE 128 96 80 96

WIRE 512 96 352 96

WIRE 80 112 80 96

WIRE -320 160 -320 64

WIRE -224 160 -320 160

WIRE -160 160 -160 64

WIRE -160 160 -224 160

WIRE 128 160 -160 160

WIRE 528 160 352 160

WIRE 576 160 528 160

WIRE -320 208 -320 160

WIRE 128 224 -112 224

WIRE 544 224 352 224

WIRE 576 224 544 224

WIRE -112 256 -112 224

WIRE 128 288 64 288

WIRE 448 288 352 288

WIRE -320 304 -320 272

WIRE 448 304 448 288

WIRE -112 368 -112 336

WIRE 448 400 448 368

WIRE -112 480 -112 432

FLAG 80 112 0

FLAG 208 -240 0

FLAG 544 224 TRIG

FLAG -320 304 0

FLAG -16 -384 VCC

FLAG -224 160 TRIG

FLAG 64 288 VCC

FLAG 448 400 0

FLAG 528 160 Discharge

FLAG 48 -272 0

FLAG -112 480 0

FLAG 512 96 VCC

FLAG -224 -208 Discharge

SYMBOL Misc\\NE555 240 192 R0

SYMATTR InstName U1

SYMBOL voltage 208 -368 R0

WINDOW 0 42 37 Left 2

WINDOW 3 45 65 Left 2

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName V1

SYMATTR Value 5

SYMBOL res -336 -368 R0

WINDOW 0 37 54 Left 2

SYMATTR InstName R1

SYMATTR Value 1K

SYMATTR SpiceLine tol=0.1

SYMBOL diode -336 -144 R0

WINDOW 0 36 34 Left 2

WINDOW 3 31 61 Left 2

SYMATTR InstName D2

SYMATTR Value 1N4148

SYMBOL polcap -336 208 R0

WINDOW 0 40 22 Left 2

WINDOW 3 39 44 Left 2

SYMATTR InstName C1

SYMATTR Value 22µ

SYMATTR Description Capacitor

SYMATTR Type cap

SYMATTR SpiceLine V=2 Irms=3 Rser=0.015 Lser=0

SYMBOL res -336 -32 R0

WINDOW 0 36 55 Left 2

SYMATTR InstName R2

SYMATTR Value 330K

SYMATTR SpiceLine tol=0.1

SYMBOL res -176 -32 R0

WINDOW 0 36 54 Left 2

SYMATTR InstName R4

SYMATTR Value 660k

SYMATTR SpiceLine tol=0.1

SYMBOL diode -144 -80 R180

WINDOW 0 -45 37 Left 2

WINDOW 3 -96 15 Left 2

SYMATTR InstName D3

SYMATTR Value 1N4148

SYMBOL cap 432 304 R0

WINDOW 0 41 21 Left 2

SYMATTR InstName C2

SYMATTR Value 0.01µf

SYMBOL polcap 32 -352 R0

WINDOW 0 39 25 Left 2

WINDOW 3 38 49 Left 2

SYMATTR InstName C3

SYMATTR Value 15µ

SYMATTR Description Capacitor

SYMATTR Type cap

SYMATTR SpiceLine V=63 Irms=1.28323 Rser=0.15 Lser=0 mfg="KEMET" pn="T521X156M063ATE150" type="Tantalum"

SYMBOL res -128 240 R0

SYMATTR InstName R3

SYMATTR Value 1k

SYMBOL LED -128 368 R0

WINDOW 0 84 37 Left 2

WINDOW 3 76 61 Left 2

SYMATTR InstName D1

SYMATTR Value NSPW500BS

TEXT 164 376 Left 2 !.tran 500sec

TEXT 736 -176 Left 2 ;Ton=0.693(R1+R2 x C)=5.04Sec

TEXT 736 -200 Left 2 ;Toff=0.693(R4 x C)=10.06