FlyingDutch

Advanced Member level 1

- Joined

- Dec 16, 2017

- Messages

- 457

- Helped

- 45

- Reputation

- 92

- Reaction score

- 55

- Trophy points

- 28

- Location

- Bydgoszcz - Poland

- Activity points

- 4,960

Hello,

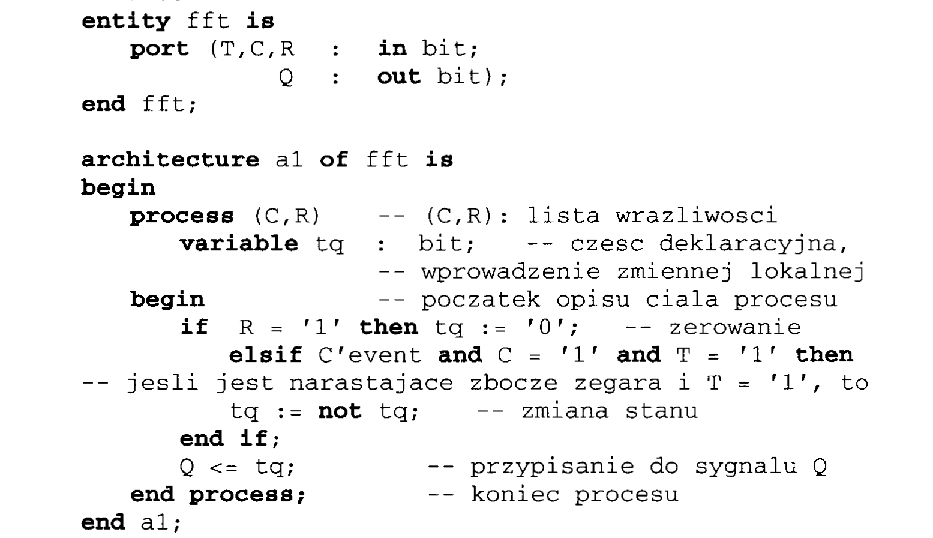

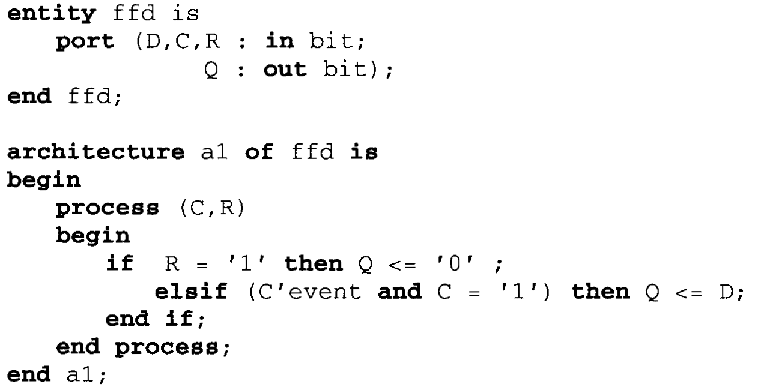

I would like to ask if somebody know about library in VHDL/Verilog with soundly designed (and optimized) primitives of "sequential logic circuits" I mean basic "bricks" for elaborating more complicated sequential circuits. I mean library/package made by one of FPGA circuits vendors like Xilinx/Intel or verified open-source one. I seen such basic primitives in Intel "Quartus" software but these primitives had been available when user was using "Schematics Editor". I am interested in such library written in one of HDL languages. I found for example such simlpe definitions of T and D flip-flops. Here are examples:

Sorry for pasting images, but this definition I only have as an image available (it is citation from polish book about VHDL).

I mean library with all kind of flip-flops, counters, various type of registers (serial/parallel), frequency dividers etc. The best would be library/package with primitives from TTL low/medium ICs or CMOS4000 series. I mean also such bricks like "reverse counters" (with asynchronic reset,set) serial-parallel registers (also shift registers), simple ALUs,

Could someone to reccomend such library/package?

Thanks in advance and regards

I would like to ask if somebody know about library in VHDL/Verilog with soundly designed (and optimized) primitives of "sequential logic circuits" I mean basic "bricks" for elaborating more complicated sequential circuits. I mean library/package made by one of FPGA circuits vendors like Xilinx/Intel or verified open-source one. I seen such basic primitives in Intel "Quartus" software but these primitives had been available when user was using "Schematics Editor". I am interested in such library written in one of HDL languages. I found for example such simlpe definitions of T and D flip-flops. Here are examples:

Sorry for pasting images, but this definition I only have as an image available (it is citation from polish book about VHDL).

I mean library with all kind of flip-flops, counters, various type of registers (serial/parallel), frequency dividers etc. The best would be library/package with primitives from TTL low/medium ICs or CMOS4000 series. I mean also such bricks like "reverse counters" (with asynchronic reset,set) serial-parallel registers (also shift registers), simple ALUs,

Could someone to reccomend such library/package?

Thanks in advance and regards

Attachments

Last edited: