ezflyr

Newbie

Hi All,

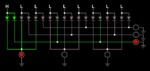

I've got a design that uses a lot of discrete logic IC's to monitor/capture 64 transient digital logic levels. The 64 logic levels are normally high, and I want to detect if any of them go low in a certain period of time. This data is then logged by a microcontroller. Currently, each logic level input goes to a flip-flop (32 total 74HC107), and then the flip-flop outputs get connected to parallel-to-serial shift registers (12 total 74HC165) in order to collect the data with a microcontroller. After the data is read, the flip-flops are reset for the next monitoring period.

I'd like to replace the discrete logic as it's becoming hard to source. At the same time I'd like to reduce my overall component count. So, I assume this design is a good candidate for CPLD?

Assuming that is correct, how do I estimate the size of the CPLD that I'll need to perform this task? Is it just about available I/O? What about required macrocells? Are flip-flops and shift registers macrocell intensive?

I'd like to select a device and start prototyping something so that I can eventually move in this direction, but at the moment I'm a complete newbie with programmable logic.

Any tips or words of wisdom?

Thanks,

John

I've got a design that uses a lot of discrete logic IC's to monitor/capture 64 transient digital logic levels. The 64 logic levels are normally high, and I want to detect if any of them go low in a certain period of time. This data is then logged by a microcontroller. Currently, each logic level input goes to a flip-flop (32 total 74HC107), and then the flip-flop outputs get connected to parallel-to-serial shift registers (12 total 74HC165) in order to collect the data with a microcontroller. After the data is read, the flip-flops are reset for the next monitoring period.

I'd like to replace the discrete logic as it's becoming hard to source. At the same time I'd like to reduce my overall component count. So, I assume this design is a good candidate for CPLD?

Assuming that is correct, how do I estimate the size of the CPLD that I'll need to perform this task? Is it just about available I/O? What about required macrocells? Are flip-flops and shift registers macrocell intensive?

I'd like to select a device and start prototyping something so that I can eventually move in this direction, but at the moment I'm a complete newbie with programmable logic.

Any tips or words of wisdom?

Thanks,

John