Lironsh

Newbie level 5

- Joined

- Oct 19, 2013

- Messages

- 10

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 100

Hello all,

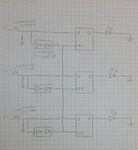

Is there a chip which includes a D FlipFlop and also a DELAYED Clock? I want to press a button and at the same time turn on an LED on the output.

My solution so far is to use a 74x175 DFF and two inverters in series from 4069 chip for the clock so i can get my t_setup on time in one press.

Anyone knows one chip for that?

Thanks,

Liron.

Is there a chip which includes a D FlipFlop and also a DELAYED Clock? I want to press a button and at the same time turn on an LED on the output.

My solution so far is to use a 74x175 DFF and two inverters in series from 4069 chip for the clock so i can get my t_setup on time in one press.

Anyone knows one chip for that?

Thanks,

Liron.