shadow_cuk

Newbie level 3

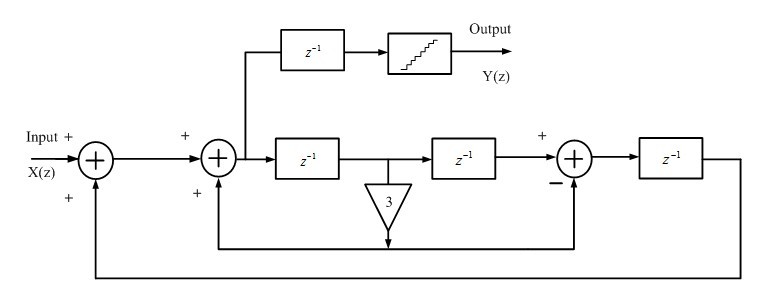

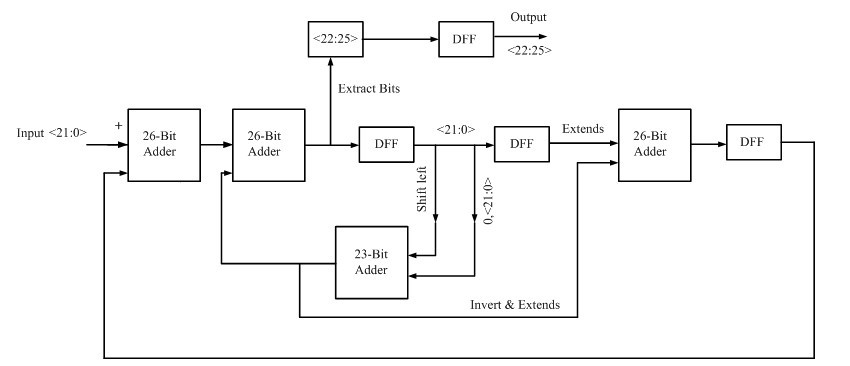

this DSM is used in a fractional-N PLL,but i dont know how to translate the signal flow graph to real circuit like the second picture,another question is how to determine the bit width of the input and output data,thx!