newbie_hs

Full Member level 1

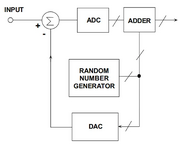

I have a 14-bit ADC. However, looking at the datasheet (see table 2 on page 5), the effective number of bits (ENOB) is always less than 12 bits.

Why is my the DAC claiming to be a 14-bit ADC when it only has 12-bit accuracy? What is the point of having two extra bits if they are meaningless?

Why is my the DAC claiming to be a 14-bit ADC when it only has 12-bit accuracy? What is the point of having two extra bits if they are meaningless?