girih192002

Full Member level 2

Hi,

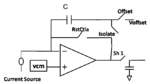

I am designing simple integrator. When Reset is going in off state. integration is starting.When Integration is started. There is dip from 2.5 V to 2 V after that integration of injected current is starting.

I did not understant why there is dip of 0.5 V.

Please, help me to understand phoenomenon. Please, go through an attached simulation waveform.

I am designing simple integrator. When Reset is going in off state. integration is starting.When Integration is started. There is dip from 2.5 V to 2 V after that integration of injected current is starting.

I did not understant why there is dip of 0.5 V.

Please, help me to understand phoenomenon. Please, go through an attached simulation waveform.