IntuitiveAnalog

Member level 2

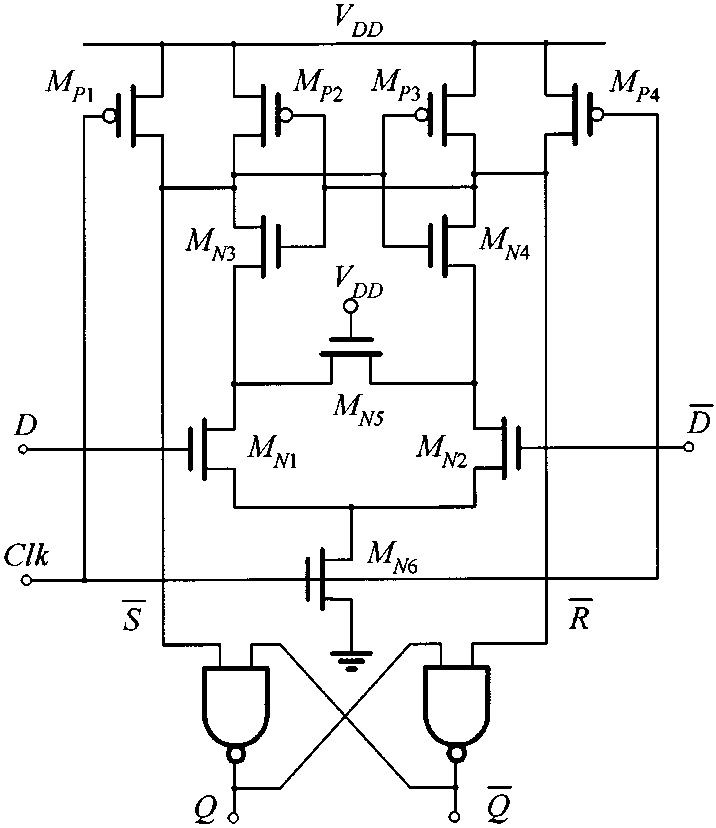

In a sense amplifier based flip flop as shown in the figure, if the data input (D) and clock input (Clk) have Vdd/2 (half the supply voltage) swing, then will it necessitate to use complementary structure instead of the shown structure (i.e. PMOS input pair and PMOS tail transistor, along with NOR based SR latch)?