saqib.shah06

Junior Member level 2

Hi Everyone,

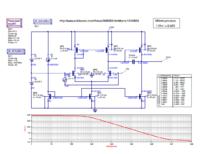

I am trying to simulate a two stage opamp (NMOS input). I am not concerned about random offset (for now I am only trying to fix systematic offset). I have the following question:

If I size the MOSFETs "perfectly" so that the bias current is exactly split between the input pair, should I still get a systematic offset? I have attached a figure in the post for your reference. I have tied sizing the MOSFETs according to what the text book says. When I apply a CM voltage of 900 mV, my output transistor (NMOS load - MN4) still remains in triode region - could anybody please explain why this happening?

Thanks for any replies.

I am trying to simulate a two stage opamp (NMOS input). I am not concerned about random offset (for now I am only trying to fix systematic offset). I have the following question:

If I size the MOSFETs "perfectly" so that the bias current is exactly split between the input pair, should I still get a systematic offset? I have attached a figure in the post for your reference. I have tied sizing the MOSFETs according to what the text book says. When I apply a CM voltage of 900 mV, my output transistor (NMOS load - MN4) still remains in triode region - could anybody please explain why this happening?

Thanks for any replies.