nealxgs

Newbie level 5

- Joined

- Mar 23, 2006

- Messages

- 8

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Activity points

- 1,341

Dear all,

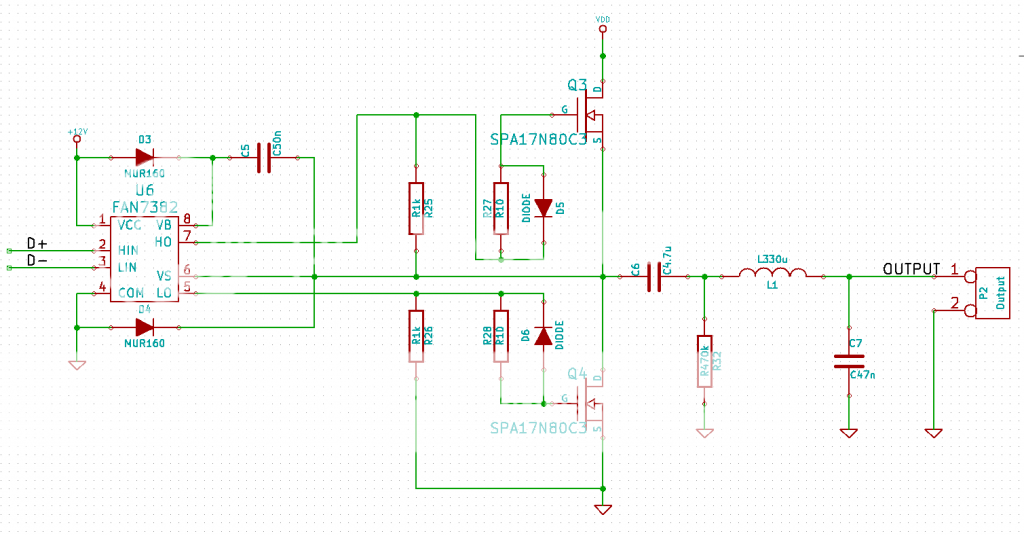

I designed a Half H bridge by a HVIC switching circuit, but I encountered some problems.

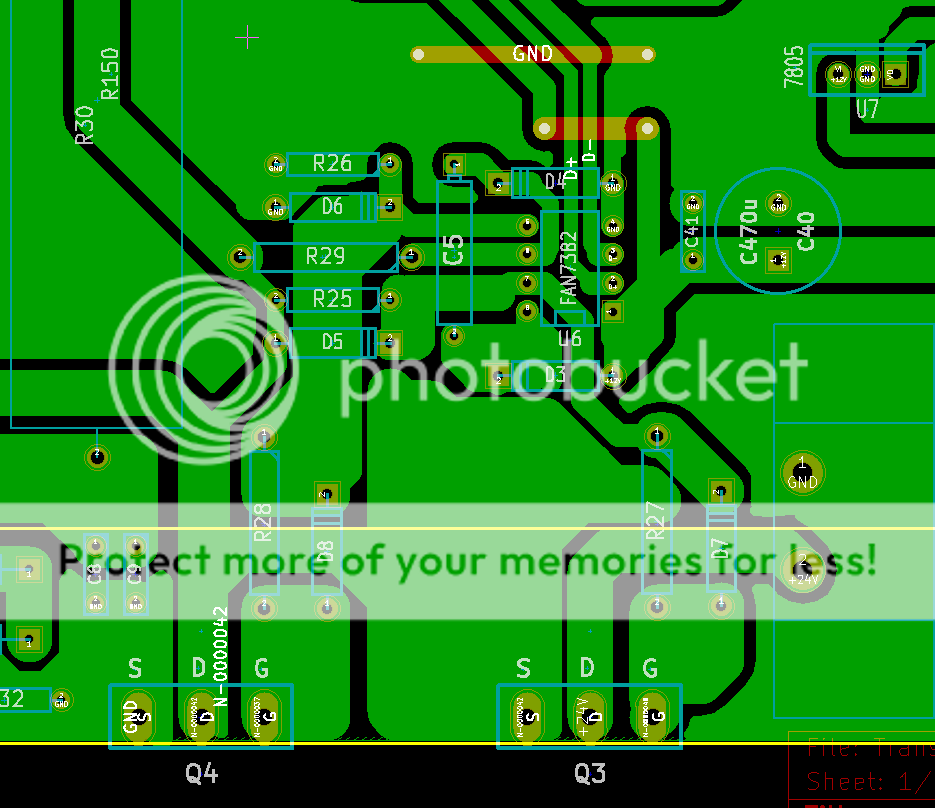

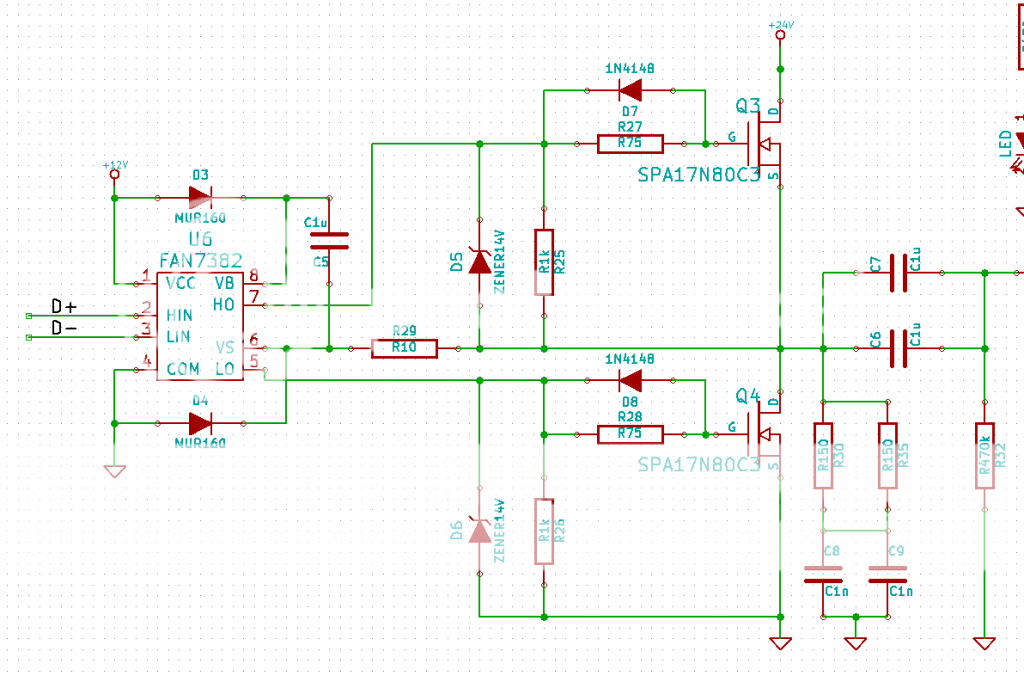

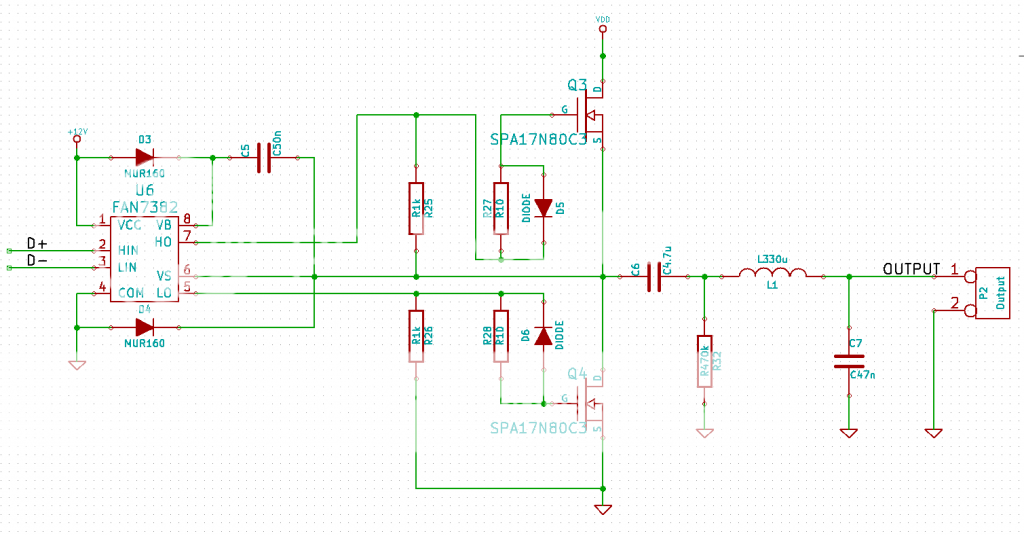

This is my schematic.

The circuit is working perfectly when I applied the VDD below 100V.

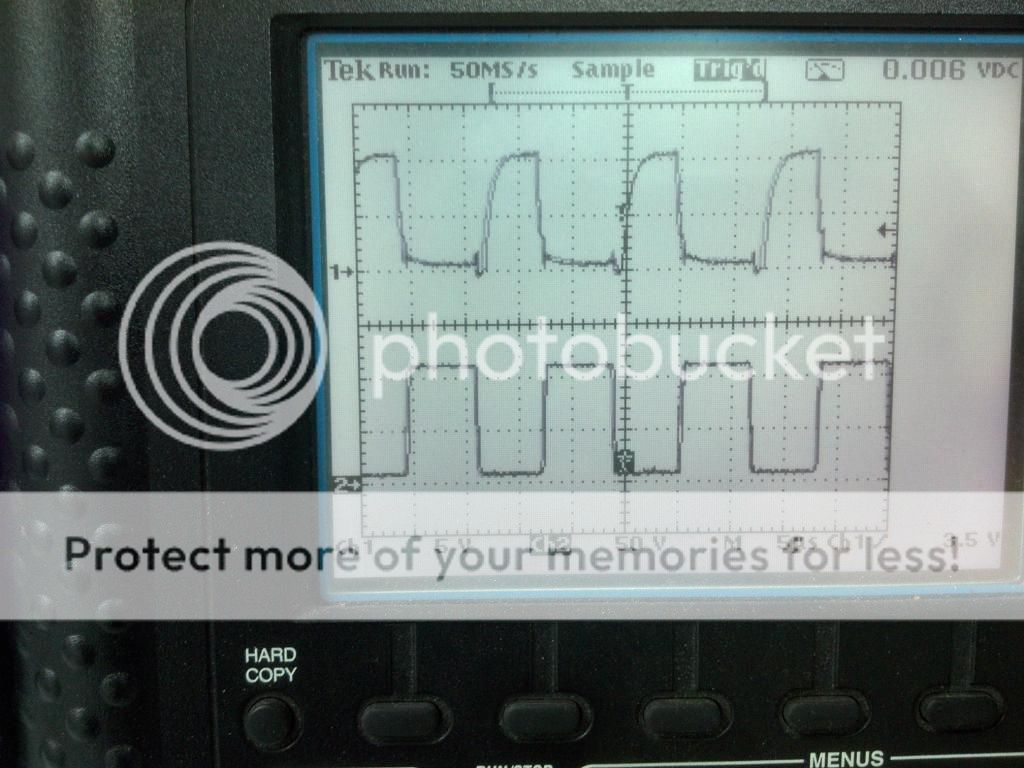

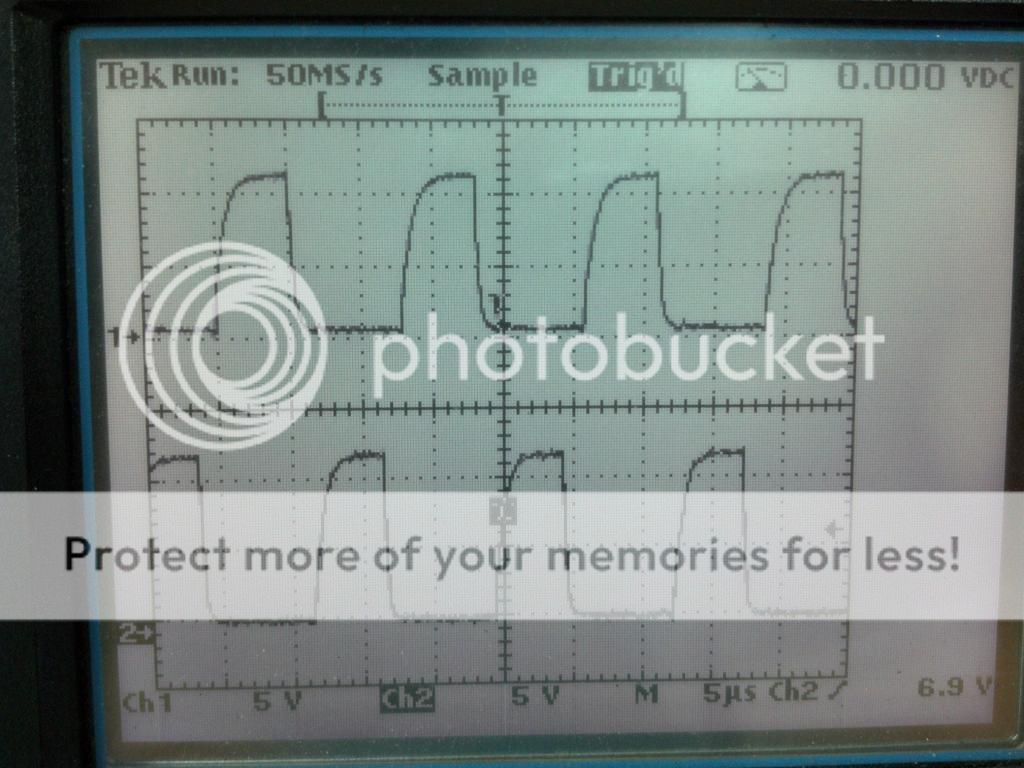

Following is the chart from oscilloscope, for the Vgs of both up-side and low-side MOSFET.

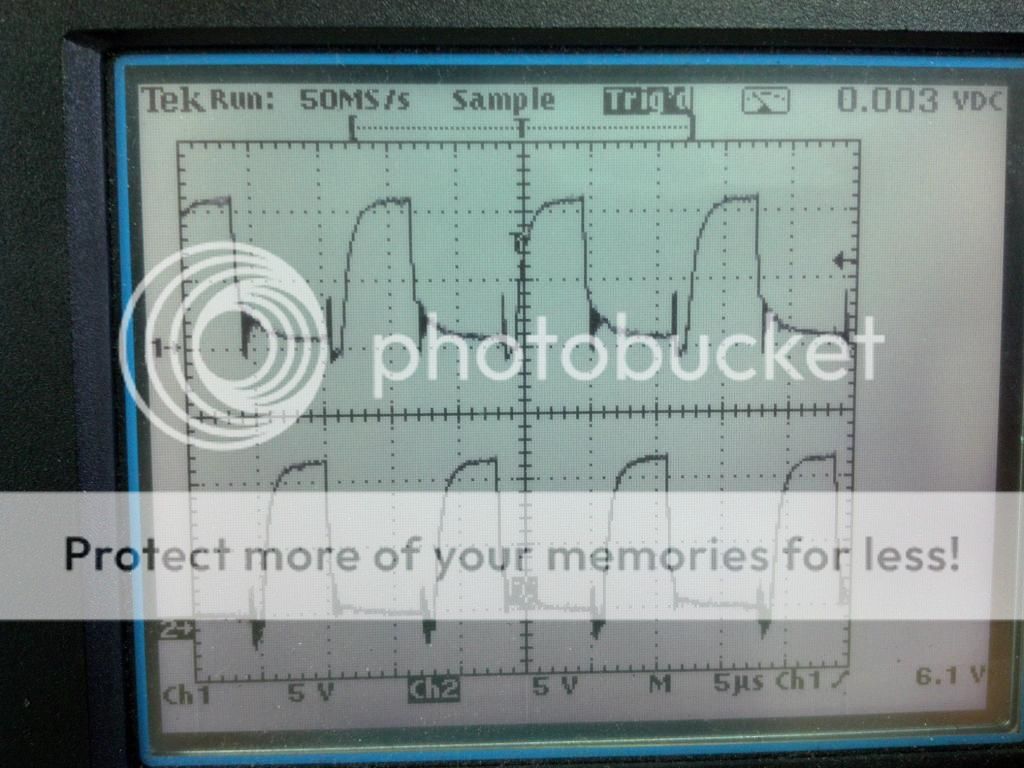

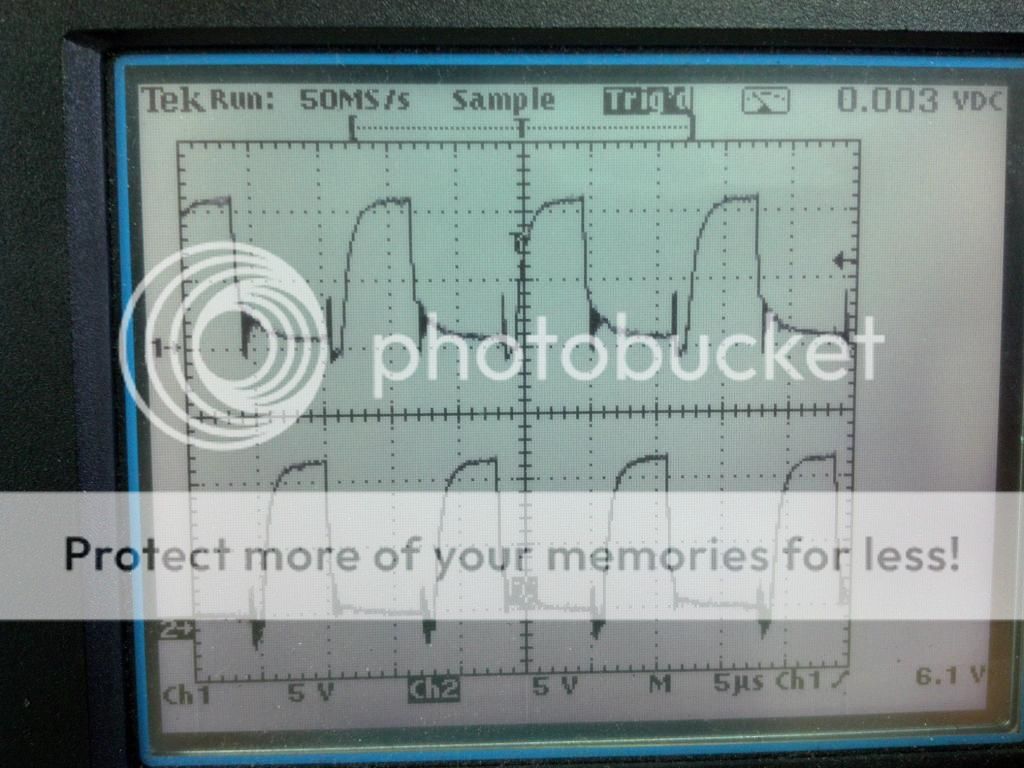

However, when I increase the VDD to 130V, the Vgs start to distort, making me be confused, as below,

when I increase the VDD more, the HVIC malfunctioned and burned.

What should I do to avoid the problem?

the HVIC I have used is NCP5106BPG, from ON-semi, and another one is FAN7382, from Fairchild.

In datasheet, they both can achieve to 600V in VDD, I think 130V is piece of cake for them.

Thanks advance for your patient and reading !

I designed a Half H bridge by a HVIC switching circuit, but I encountered some problems.

This is my schematic.

The circuit is working perfectly when I applied the VDD below 100V.

Following is the chart from oscilloscope, for the Vgs of both up-side and low-side MOSFET.

However, when I increase the VDD to 130V, the Vgs start to distort, making me be confused, as below,

when I increase the VDD more, the HVIC malfunctioned and burned.

What should I do to avoid the problem?

the HVIC I have used is NCP5106BPG, from ON-semi, and another one is FAN7382, from Fairchild.

In datasheet, they both can achieve to 600V in VDD, I think 130V is piece of cake for them.

Thanks advance for your patient and reading !