Hawaslsh

Full Member level 3

- Joined

- Mar 13, 2015

- Messages

- 167

- Helped

- 5

- Reputation

- 10

- Reaction score

- 7

- Trophy points

- 1,298

- Location

- Washington DC, USA

- Activity points

- 3,461

Hello all,

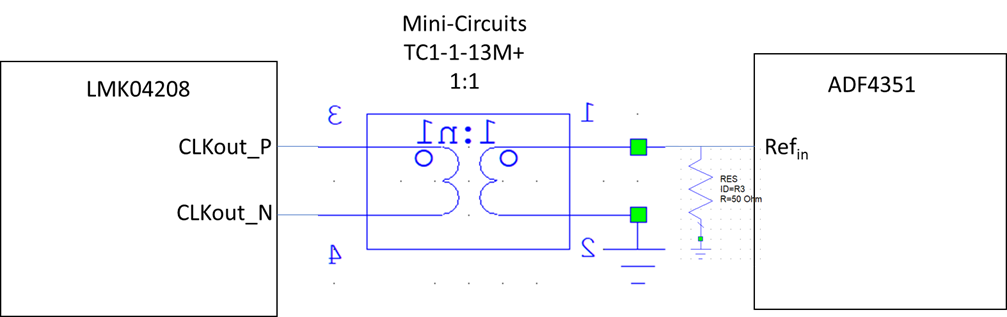

I am wondering what's the proper way to terminate a differential clock signal through a transformer into a single ended reference for a PLL. I've read through a few Ti application notes on the issue, but I am still a bit confused. The picture above is the diagram of what I am trying to accomplish. To generate a reference clock, there is a Ti clock distribution chip (LMK04208) creating a differential clock signal. The chip is capable of producing different types of clock outputs: LVDS, LVPECL, and LVCMOS. The PLL is an analog devices ADF4351, which has a single ended reference input. From the ADF4351 datasheet: "Reference Input. This CMOS input has a nominal threshold of AV DD /2 and a dc equivalent input resistance of 100 kΩ. This input can be driven from a TTL or CMOS crystal oscillator, or it can be ac-coupled"

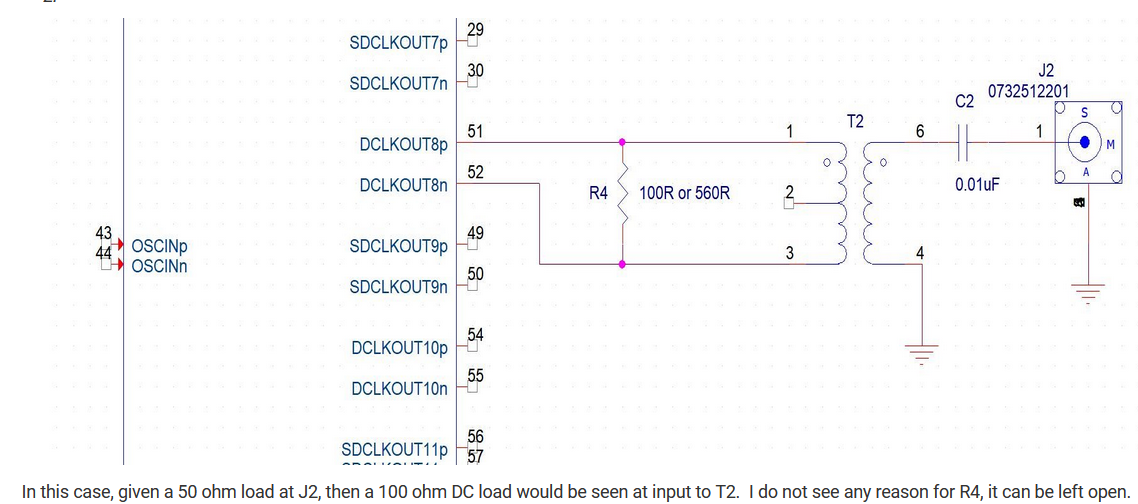

There was a useful thread on the Ti design support forum about this topic, and one of the Ti folks recommended using a Mini-Circuits 1:1 transformer, TC1-1-13M+. However, the load in that case was 50 Ohms, not a high resistance CMOS input. In the case of the 50ohm load, the Ti rep said:

Does that imply I can simply terminate the single ended side with a 50ohm resistor placed close to the ADF4351 reference input? Is this value (or invalid) for all the different output types? If the 1:1 transformer can be terminated in 50 Ohms, does that imply I need to use 50 ohm differential impedance lines from the LMK04208 output to the transofmer as well as a 50 ohm line from the transformer to the ADF4351?

Any advice on the matter would be greatly appreciated,

Thanks in advance,

Sami

I am wondering what's the proper way to terminate a differential clock signal through a transformer into a single ended reference for a PLL. I've read through a few Ti application notes on the issue, but I am still a bit confused. The picture above is the diagram of what I am trying to accomplish. To generate a reference clock, there is a Ti clock distribution chip (LMK04208) creating a differential clock signal. The chip is capable of producing different types of clock outputs: LVDS, LVPECL, and LVCMOS. The PLL is an analog devices ADF4351, which has a single ended reference input. From the ADF4351 datasheet: "Reference Input. This CMOS input has a nominal threshold of AV DD /2 and a dc equivalent input resistance of 100 kΩ. This input can be driven from a TTL or CMOS crystal oscillator, or it can be ac-coupled"

There was a useful thread on the Ti design support forum about this topic, and one of the Ti folks recommended using a Mini-Circuits 1:1 transformer, TC1-1-13M+. However, the load in that case was 50 Ohms, not a high resistance CMOS input. In the case of the 50ohm load, the Ti rep said:

Does that imply I can simply terminate the single ended side with a 50ohm resistor placed close to the ADF4351 reference input? Is this value (or invalid) for all the different output types? If the 1:1 transformer can be terminated in 50 Ohms, does that imply I need to use 50 ohm differential impedance lines from the LMK04208 output to the transofmer as well as a 50 ohm line from the transformer to the ADF4351?

Any advice on the matter would be greatly appreciated,

Thanks in advance,

Sami