Mike28

Newbie level 1

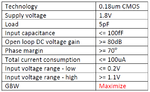

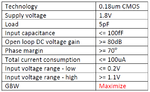

So I am trying to design an OTA to meet the following specs:

Plus the following constraints:

The maximum allowed transistor width is W=100um.

The maximum allowed transistor length is L=20um.

The maximum allowed capacitance (if you use Miller compensation) is Cc=2pF.

The supplies are Vss=0 & Vdd=1.8V.

______________________________________________________________________________

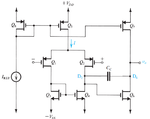

I decided to go with the typical 2 stage miller OTA:

and the best result I got was (while meeting the specs) GBW = 20 MHZ.

______________________________________________________________________________

NOTE: I checked few posts in the forum, and I saw a lot of designers suggest using the RFC OTA. I checked it and its design seems to be 10 times harder than the Miller OTA (I am still new to the analog design :grin

Plus the following constraints:

The maximum allowed transistor width is W=100um.

The maximum allowed transistor length is L=20um.

The maximum allowed capacitance (if you use Miller compensation) is Cc=2pF.

The supplies are Vss=0 & Vdd=1.8V.

______________________________________________________________________________

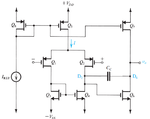

I decided to go with the typical 2 stage miller OTA:

and the best result I got was (while meeting the specs) GBW = 20 MHZ.

______________________________________________________________________________

- Is the miller OTA suitable for this design problem?

- Is there any rule of thumb on choosing the transistor's W and L?

- What is the maximum GBW that I can achieve while meeting the specs? (this will help decide if my design was okay, at least.)

NOTE: I checked few posts in the forum, and I saw a lot of designers suggest using the RFC OTA. I checked it and its design seems to be 10 times harder than the Miller OTA (I am still new to the analog design :grin

Last edited: