eagleboy

Newbie level 1

- Joined

- Nov 29, 2012

- Messages

- 1

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,288

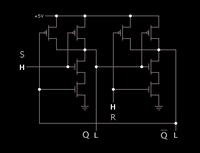

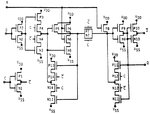

How to design CMOS D clocked Flip-flop with CLEAR input?

Hi,

I am looking for a GATE/transistor level design of a D-flip-flop where I would have three inputs, i.e. D, CLK and CLEAR, and two outputs Q and Q'.

I am not a digital guy so don't know much about these Latches/flip-flops....So please help me in this regard.

Regards.

Hi,

I am looking for a GATE/transistor level design of a D-flip-flop where I would have three inputs, i.e. D, CLK and CLEAR, and two outputs Q and Q'.

I am not a digital guy so don't know much about these Latches/flip-flops....So please help me in this regard.

Regards.

Last edited: