avner_g

Junior Member level 2

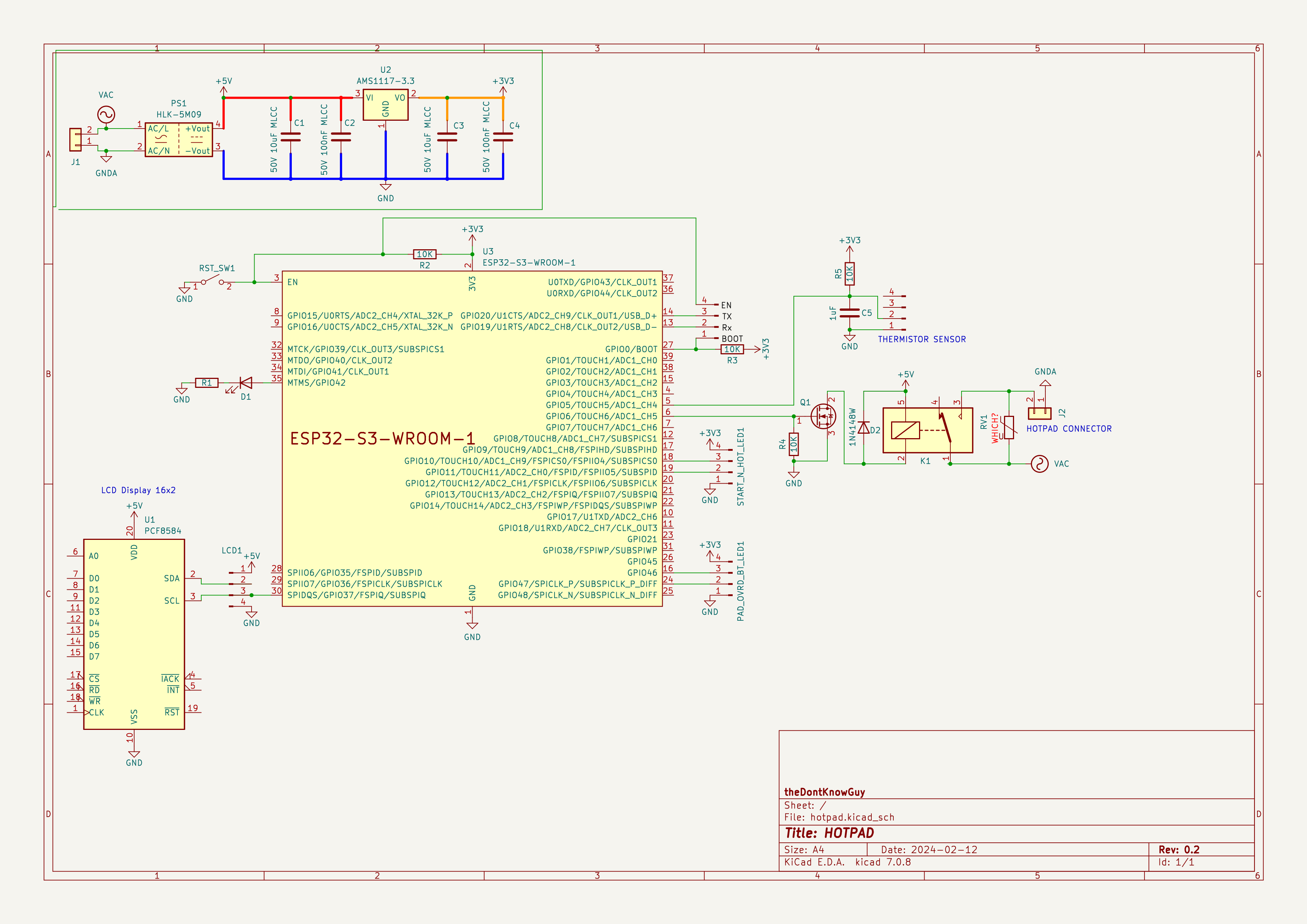

I am building an SMD soldering hot plate station. I got good results when prototyping this, using this guy, which is a 100x200 500W.

Since I am a novice, definitely in 220V, I wanted a hint on how to protect the components against bursts when the relay disconnects the hot pad.

I see some disturbances on the LCD on disconnections.

I thought of putting a veristor on the hot pad clamps, not sure what spec it should be (and if it is helpful).

Also, any other advice would be welcomed.

(Grounding of the hot pad is not illustrated here but is planned.)

Since I am a novice, definitely in 220V, I wanted a hint on how to protect the components against bursts when the relay disconnects the hot pad.

I see some disturbances on the LCD on disconnections.

I thought of putting a veristor on the hot pad clamps, not sure what spec it should be (and if it is helpful).

Also, any other advice would be welcomed.

(Grounding of the hot pad is not illustrated here but is planned.)