diaz080

Member level 4

- Joined

- Oct 3, 2012

- Messages

- 73

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Activity points

- 1,714

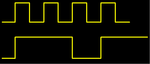

how to design a circuit which generate output which is high for 2 clock cycles and low for 1 clock cycle repeatedly