fuxinmingming

Member level 1

Hi guys,

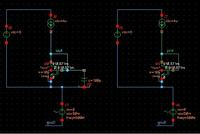

When we use current mirror, usually we add bypass capacitance to reduce bias branch's noise.

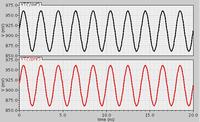

For example, if I add 500fF bypass capacitance, total noise will be reduced by almost 10 times(noise=kT/C, capacitance increased almost by 10 times).

My question is:

How should I choose this bypass capacitance? Is it semiempirical? Is it 500fF capacitance ok? Or how do I calculate its value?

Regards,

Ming

When we use current mirror, usually we add bypass capacitance to reduce bias branch's noise.

For example, if I add 500fF bypass capacitance, total noise will be reduced by almost 10 times(noise=kT/C, capacitance increased almost by 10 times).

My question is:

How should I choose this bypass capacitance? Is it semiempirical? Is it 500fF capacitance ok? Or how do I calculate its value?

Regards,

Ming