joelam

Newbie level 3

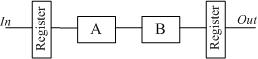

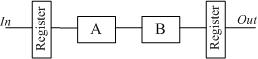

Consider the circuit of Figure 2. Module A and B have a delay of 20nsec and 65nsec at 5V, and switching 30pF and 112pF respectively. The register has a delay of 4nsec and switches 0.2pF. Adding a pipeline register allows for reduction of the supply voltage while maintaining throughput. How much power can be saved this way? Here, you can approximate the delay is inverse proportional to the supply voltage, while the relationship between power consumption and voltage, switch capacitance and throughput can be expressed as P=CV2f .

Last edited by a moderator: