Awalluddin

Newbie level 5

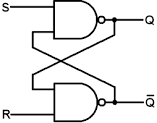

Hi everyone, an SR latch that build using Nand gate, how do the simulator decide the Q and QBar terminal. The SR latch is symmetry, and either the terminal could be Q and vice versa.

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.