Xenon02

Full Member level 3

Hello !

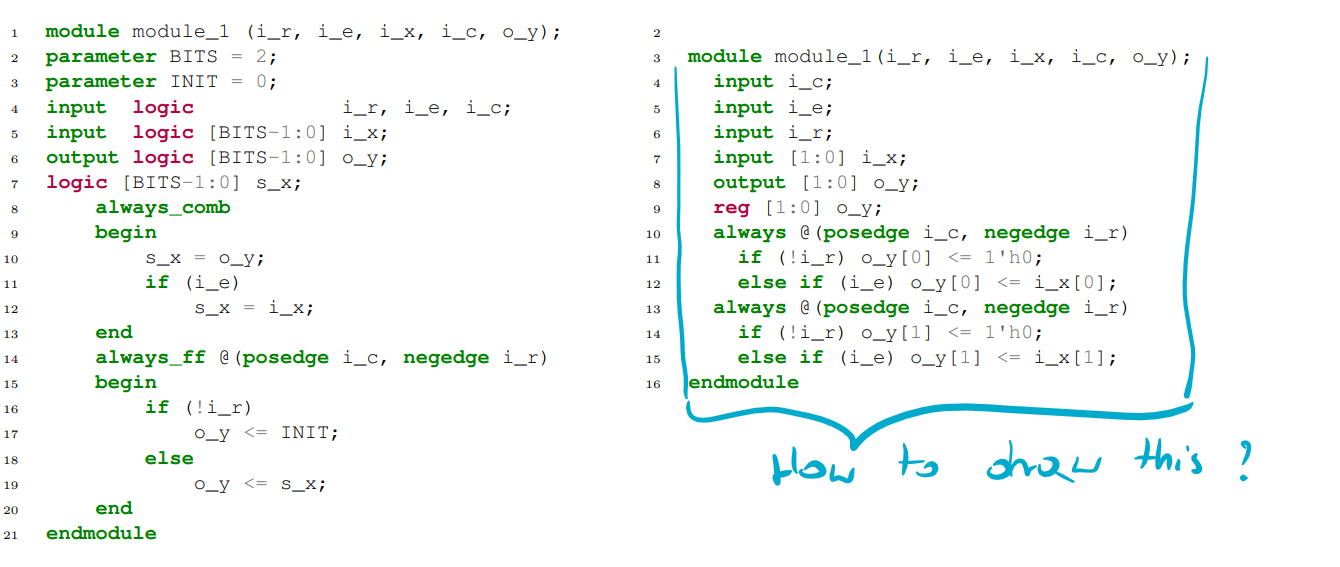

I've got a problem because I was asked to draw what synthezis dropped like in the picture using logic gates and D-flip/flop with set/reset.

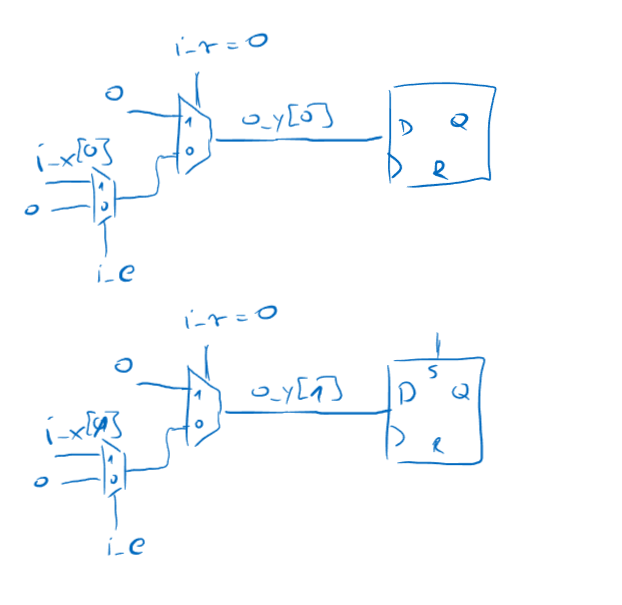

I tried to draw this :

I tried to draw this but it didn't have sense.

But at the end I've got like reset in multiplexer and reset in D-flipflop.

How do I interpret the "if else" command ? It is not a multiplexer I guess ?

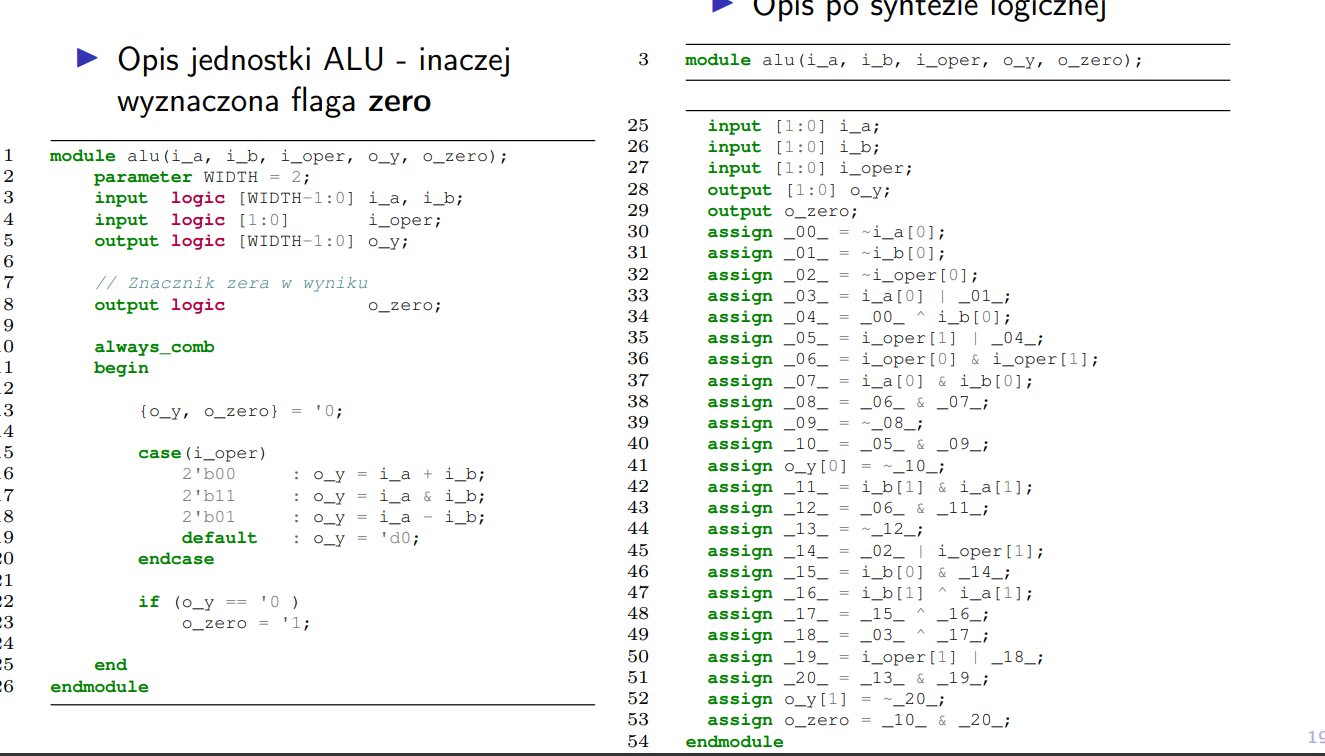

I know that multiplexer looked like that after the yosys synthesiz :

I've got a problem because I was asked to draw what synthezis dropped like in the picture using logic gates and D-flip/flop with set/reset.

I tried to draw this :

I tried to draw this but it didn't have sense.

But at the end I've got like reset in multiplexer and reset in D-flipflop.

How do I interpret the "if else" command ? It is not a multiplexer I guess ?

I know that multiplexer looked like that after the yosys synthesiz :