trapoe

Member level 3

hv high speed switch

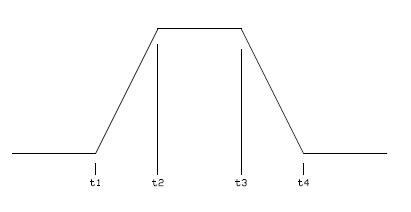

I need a switch quite special to connect a 400 V to a load (50 pF // 5,6 MΩ). The rise time has to be less than 30 ns.

I would use medium power MOS, N channel. Anyone has already seen something like this ?

I need a switch quite special to connect a 400 V to a load (50 pF // 5,6 MΩ). The rise time has to be less than 30 ns.

I would use medium power MOS, N channel. Anyone has already seen something like this ?