mpig09

Full Member level 4

- Joined

- Aug 26, 2005

- Messages

- 232

- Helped

- 8

- Reputation

- 16

- Reaction score

- 2

- Trophy points

- 1,298

- Location

- Taipei

- Activity points

- 2,810

Hi all:

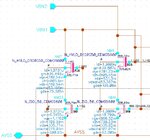

I am design a current mirror, and this circuit is used in a LDO,

so the quiescent current needs to small.

But I found the W/L of the high voltage MOS(NM5 and NM7) is big (20u/1.6u), so the NM5 and NM7 can't into the sat. region when the current is small (< 5uA).

Could you give me some suggestion?

(other structure or design note for the attached file and ...)

Thanks.

mpig

I am design a current mirror, and this circuit is used in a LDO,

so the quiescent current needs to small.

But I found the W/L of the high voltage MOS(NM5 and NM7) is big (20u/1.6u), so the NM5 and NM7 can't into the sat. region when the current is small (< 5uA).

Could you give me some suggestion?

(other structure or design note for the attached file and ...)

Thanks.

mpig