liucheng311

Junior Member level 3

dear everyone

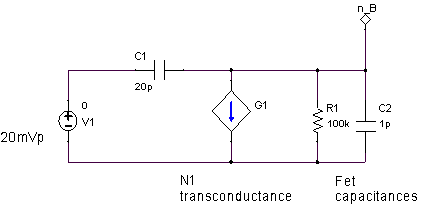

i want to know about zeros of circuit,so i build a circuit shown below:the capacitance of C1 is about 20pF;V1 is a sin signal,its offset voltage is 1V,and its amplitude voltage is 10mV.when the frequency of V1 is higher than about 1MHZ,the voltage at node B is a sin wave,whose peak-peak value is 20mV,and the higher peak voltage is 1.92V,which is the operating point.

i know at higher frequency,the capacitor will short the gate and node B,but why is the higher peak voltage at node B at its operating point?

i want to know about zeros of circuit,so i build a circuit shown below:the capacitance of C1 is about 20pF;V1 is a sin signal,its offset voltage is 1V,and its amplitude voltage is 10mV.when the frequency of V1 is higher than about 1MHZ,the voltage at node B is a sin wave,whose peak-peak value is 20mV,and the higher peak voltage is 1.92V,which is the operating point.

i know at higher frequency,the capacitor will short the gate and node B,but why is the higher peak voltage at node B at its operating point?