Bou

Full Member level 3

Hello,

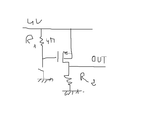

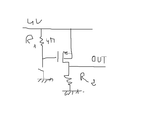

I designed the schematic (picture attached) , and my question is about the pull up resistor R1 when I choose a value of 4MOhms I notice that there is a difference of voltage of 1 V between the supply (4V) and the gate of the PMOS and this difference is reduced when I decrease the value of R1 (0.5 V for 1.5 Mohms), is this due to the leakage current of the gate?? is that normal? I think that the gate current is very low and I should have the same voltage (4 V)at the gate!!!!!

I designed the schematic (picture attached) , and my question is about the pull up resistor R1 when I choose a value of 4MOhms I notice that there is a difference of voltage of 1 V between the supply (4V) and the gate of the PMOS and this difference is reduced when I decrease the value of R1 (0.5 V for 1.5 Mohms), is this due to the leakage current of the gate?? is that normal? I think that the gate current is very low and I should have the same voltage (4 V)at the gate!!!!!