MZulkarnain Jaranee

Newbie level 5

- Joined

- Nov 27, 2014

- Messages

- 8

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 70

Problem in Gasp Pipeline Controller in VHDL

Hi everyone,

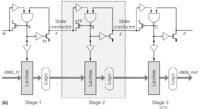

I'm working on the Gasp Controller as shown within the red area in the image attachment 111734. I did the code but the problem is the result didn't display as what show in the below image. Could anyone please advice/assist on this.

**broken link removed**

Here is the code

Here is the netlist viewer result :

**broken link removed**

In the netlist viewer, the n_out, p_out and en all connected to input wire before y.

Hi everyone,

I'm working on the Gasp Controller as shown within the red area in the image attachment 111734. I did the code but the problem is the result didn't display as what show in the below image. Could anyone please advice/assist on this.

**broken link removed**

Here is the code

Code:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY gaspblock IS

PORT

(

x,y : inout STD_LOGIC;

en : out STD_LOGIC;

n_Out, p_out: buffer STD_LOGIC

);

END gaspblock;

ARCHITECTURE bdf_type OF gaspblock IS

signal B, yy, a : std_LOGIC;

BEGIN

B <= ((not x) nand y);

en <= not B;

a <= not B;

yy <= B;

---- n- transistor ------

process(a)

begin

case a is

when '0' | 'L' => n_Out <= '1';

when '1' | 'H' => n_Out <= '0';

when others => n_Out <= 'X';

end case;

end process;

------ p -transistor ------

process(yy)

variable control: std_Logic;

begin

case yy is

when '0' | 'L' => p_out <= '1';

when '1' | 'H' => p_out <= '0';

when others => p_out <= 'X';

end case;

end process;

x <= p_out;

y <= n_Out;

END bdf_type;Here is the netlist viewer result :

**broken link removed**

In the netlist viewer, the n_out, p_out and en all connected to input wire before y.

Last edited: