GagarinMolotov

Newbie level 3

- Joined

- Jun 7, 2013

- Messages

- 4

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,309

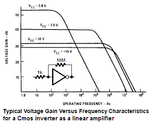

Does anybody know how increasing / decreasing in Vdd affects gain of the cmos inverter(Wp = 2Wmin W n = 1Wmin) ? It is pretty hard nut to *****