junhao

Junior Member level 2

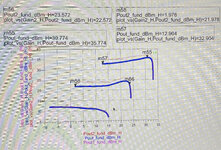

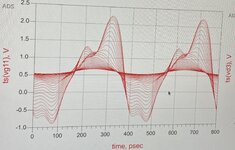

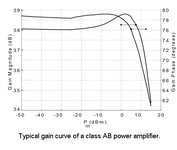

嗨,我在设计功率放大器时看到了 5dB 的增益扩展,栅极电压显示 MOSFET 在深度 AB 类中工作。我不希望这种增益扩大,但我不知道如何减少这种现象。请问你能帮帮我吗?

[Betwixt] For the benefit of non-Chinese speakers, it translates as:

Hi, I saw a gain extension of 5dB when designing a power amplifier, and the gate voltage shows that the MOSFET is working in deep class AB. I don't want this gain to expand, but I don't know how to reduce this phenomenon. Could you please help me?

[Betwixt] For the benefit of non-Chinese speakers, it translates as:

Hi, I saw a gain extension of 5dB when designing a power amplifier, and the gate voltage shows that the MOSFET is working in deep class AB. I don't want this gain to expand, but I don't know how to reduce this phenomenon. Could you please help me?

Last edited by a moderator: