user0088

Junior Member level 3

Please help in providing some information/document for fully differential current-steering DAC structure.

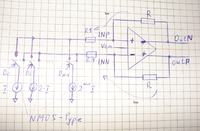

I mean a structure, where after current sources a fully differential amplifier is used, which outputs vary over common-mode voltage (both up and down directions).

In a case of using structure shown in attached file, both outputs of a differential amplifier (OUTP and OUTN) will always be below from some common-mode voltage, independent on the input digital code (D0,D1,...).

So, how to have a fully differential outputs? I have searched a lot, but I haven't found any helpful information.

I think, that both PMOS and NMOS types current sources can be used for this purpose, but.......I guess the mismatches will greatly effect on DAC performance.

I want to know how is getting fully differential current-steering DAC in practice.

Thanks in advance.

I mean a structure, where after current sources a fully differential amplifier is used, which outputs vary over common-mode voltage (both up and down directions).

In a case of using structure shown in attached file, both outputs of a differential amplifier (OUTP and OUTN) will always be below from some common-mode voltage, independent on the input digital code (D0,D1,...).

So, how to have a fully differential outputs? I have searched a lot, but I haven't found any helpful information.

I think, that both PMOS and NMOS types current sources can be used for this purpose, but.......I guess the mismatches will greatly effect on DAC performance.

I want to know how is getting fully differential current-steering DAC in practice.

Thanks in advance.