cupoftea

Advanced Member level 5

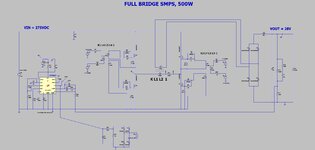

Hi,

Just seen a Full Bridge with Vin = 200Vdc. (output of 115VAC PFC)

Fsw = 47kHz.

Its gate drive is two pulse transformers each with 2 secs........for each leg......bipolar drive....in each secondary is only a 12R series resistor and 12k gate_source res.

No gate zener (back to back)

Would you think this was unadviseable?

Just seen a Full Bridge with Vin = 200Vdc. (output of 115VAC PFC)

Fsw = 47kHz.

Its gate drive is two pulse transformers each with 2 secs........for each leg......bipolar drive....in each secondary is only a 12R series resistor and 12k gate_source res.

No gate zener (back to back)

Would you think this was unadviseable?