sarmad88

Junior Member level 2

- Joined

- Feb 12, 2013

- Messages

- 20

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,474

help me please

in my design this error appear in place and route step

tha target device is spartan 3e and the ise is ise14.1

error: Place:120 - There were not enough sites to place all selected components.

Some of these failures can be circumvented by using an alternate algorithm (though it may take longer run time). If

you would like to enable this algorithm please set the environment variable XIL_PAR_ENABLE_LEGALIZER to 1 and try

again

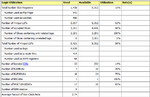

and the utilization summary is show below:

why this error occurs and how can overcome this error please?

in my design this error appear in place and route step

tha target device is spartan 3e and the ise is ise14.1

error: Place:120 - There were not enough sites to place all selected components.

Some of these failures can be circumvented by using an alternate algorithm (though it may take longer run time). If

you would like to enable this algorithm please set the environment variable XIL_PAR_ENABLE_LEGALIZER to 1 and try

again

and the utilization summary is show below:

why this error occurs and how can overcome this error please?

Last edited: