wsobhan

Newbie level 3

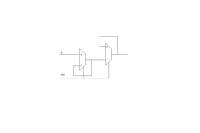

Hello all, was hoping someone could help me out with this. I'm trying to figure out how to design a D flip flop using nothing but 2:1 mux(s). Nothing else allowed.

I can see how a latch can be designed using a 2:1 mux where the output responds instantly to the input based on the select line. however, to do this for a flop, one would think you would need some kind of rising edge detect circuitry? Can anyone elaborate? Thanks!

I can see how a latch can be designed using a 2:1 mux where the output responds instantly to the input based on the select line. however, to do this for a flop, one would think you would need some kind of rising edge detect circuitry? Can anyone elaborate? Thanks!

[/

[/