Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

No, it only ensures that you will be at the border between

linear and saturation. The inversion "strength" depends on

the current being thrown at it.

There's not much "advantage" to weak inversion, it is just

where you end up when trying to do low power analog.

Or operate at low voltages (for reasons of chasing low

power, usually).

For FETs that are not tied D-G, some DC attributes

improve at lower Vgs (like Rout / gDS) and some get

worse (like gm) when you operate lower than VT0.

And things like AC bandwidth suffer quite a bit.

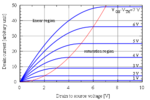

look at the transistor curve, the different levels of current is controlled by VGS-Vth. View attachment 140825