sp3

Member level 5

Hi all,

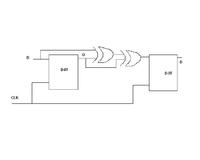

I have a digital design question here.. Please look at the attachment..

I have the input for DFF as D. later this input is XORed with the Q (output of DFF). The XOR output is passed to a unkown circuitry so that I get the original input D. Now anyone of guys please let me what is the unkown circuit here ??

Thanks,

sp3

I have a digital design question here.. Please look at the attachment..

I have the input for DFF as D. later this input is XORed with the Q (output of DFF). The XOR output is passed to a unkown circuitry so that I get the original input D. Now anyone of guys please let me what is the unkown circuit here ??

Thanks,

sp3