hellotheworld

Newbie

Hello !

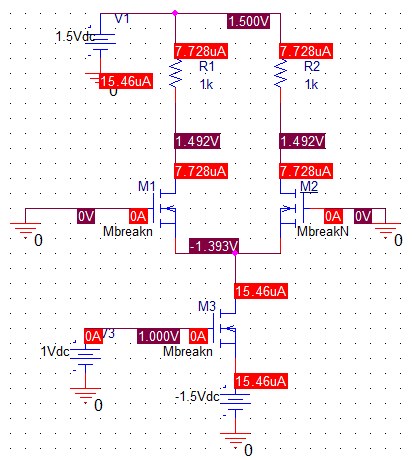

The image below is the simulation of my differential amplifier in dc analysis in pspice.

I struggled in finding the currents for \[ I_{d1}, I_{d2}, I_{d3} \]

I tried use \[ I_{d}=\frac{K_{n}}{2}(V_{GS}-V_{TN})^2 \] but I can't find the values as well as simulation does.

I also tried to find \[ V_{s1} \] by using \[ I_{d1}+I_{d2}=I_{d3} \] and then \[ I_{d}=\frac{K_{n}}{2}(V_{GS}-V_{TN})^2 \], but the final result does not match \[ V_{s1} \] in simulation.

In this simulation, assuming .model Mbreakn NMOS VTO=1 KP=100u LAMBDA=0 W=1u L=1u

The image below is the simulation of my differential amplifier in dc analysis in pspice.

I struggled in finding the currents for \[ I_{d1}, I_{d2}, I_{d3} \]

I tried use \[ I_{d}=\frac{K_{n}}{2}(V_{GS}-V_{TN})^2 \] but I can't find the values as well as simulation does.

I also tried to find \[ V_{s1} \] by using \[ I_{d1}+I_{d2}=I_{d3} \] and then \[ I_{d}=\frac{K_{n}}{2}(V_{GS}-V_{TN})^2 \], but the final result does not match \[ V_{s1} \] in simulation.

In this simulation, assuming .model Mbreakn NMOS VTO=1 KP=100u LAMBDA=0 W=1u L=1u

Last edited: