niteshtripathi

Member level 3

Hi all,

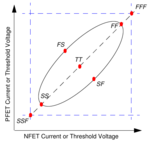

As we know in FF and FS (corner notation), first letter corresponds to the NMOS device while the second with PMOS device.

While characterizing only NMOS device, I found that Id vs Vds plot is different for FF and FS while it should be same because in both corners the NMOS is Fast only.

Any leads will be helpful. thanks.

As we know in FF and FS (corner notation), first letter corresponds to the NMOS device while the second with PMOS device.

While characterizing only NMOS device, I found that Id vs Vds plot is different for FF and FS while it should be same because in both corners the NMOS is Fast only.

Any leads will be helpful. thanks.