Boyenju

Newbie level 2

- Joined

- Aug 18, 2013

- Messages

- 2

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 13

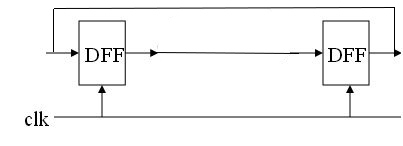

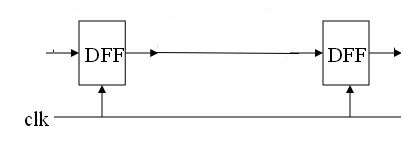

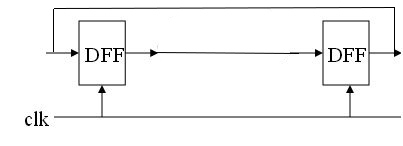

I have two types of circuits

Type 1

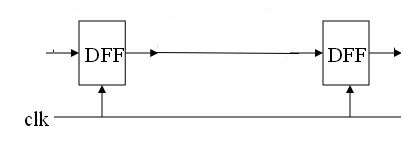

Type2

I was told that i have hold violation in the 2nd DFF(right one) in both of them, where would you put buffers in order to solve the hold violation?

i would be very happy if some explain me this with an clk diagram or smthing.

thank you.

Type 1

Type2

I was told that i have hold violation in the 2nd DFF(right one) in both of them, where would you put buffers in order to solve the hold violation?

i would be very happy if some explain me this with an clk diagram or smthing.

thank you.