r.mirtaji

Junior Member level 3

Dear friends,

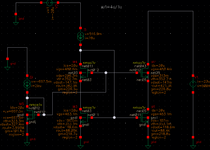

I attached you the picture of the wide swing current mirror and here is my question please,

We know that current mirror sources use to copy current (W / L ratio) from one circuit block to another

without the resistance of the next block affecting this current transfer

The following factors are important to us when designing a current source:

1-Output impedance

2-maximum swing

*3-wide current range

Is it possible to design a wide swing current mirror that the output current follows a wide range of input currents?

The wide swing current mirror is usually designed to produce a constant current with a coefficient relative to the input current.

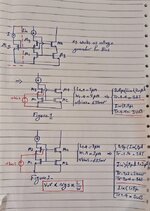

In the figure below, when the input current is between 4uA and 20uA, all transistors operate in the saturation region.

But when the current is less than 4uA. First, the M4 enters the linear region And at lower currents, the transistors M1,M2,M3 enter the sub-threshold region.

1-Can the circuit be designed that in the lower current all transistors are in the saturation region and the wide swing current mirror has more wide range?

2-Is the operation of the circuit correct even though the transistors are in currents of less than 4 that enter the sub-region and the operation of the circuit is acceptable?

I attached you the picture of the wide swing current mirror and here is my question please,

We know that current mirror sources use to copy current (W / L ratio) from one circuit block to another

without the resistance of the next block affecting this current transfer

The following factors are important to us when designing a current source:

1-Output impedance

2-maximum swing

*3-wide current range

Is it possible to design a wide swing current mirror that the output current follows a wide range of input currents?

The wide swing current mirror is usually designed to produce a constant current with a coefficient relative to the input current.

In the figure below, when the input current is between 4uA and 20uA, all transistors operate in the saturation region.

But when the current is less than 4uA. First, the M4 enters the linear region And at lower currents, the transistors M1,M2,M3 enter the sub-threshold region.

1-Can the circuit be designed that in the lower current all transistors are in the saturation region and the wide swing current mirror has more wide range?

2-Is the operation of the circuit correct even though the transistors are in currents of less than 4 that enter the sub-region and the operation of the circuit is acceptable?