noor84

Member level 5

Hi all,

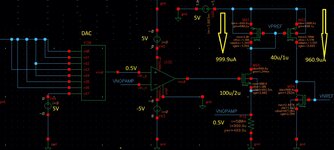

Please, I am going to design the current mirror as in the circuit shown in the attached picture, I have a problem with my circuit that is:

I can not get the same current in the other branch as shown in the picture.

Could you please help me to solve this problem?

Note: the dimensions of W and L for the transistors are shown and I selected them based on trial and error to get these results. Is there any rule to follow to select the best transistor dimensions?

Regards.

Please, I am going to design the current mirror as in the circuit shown in the attached picture, I have a problem with my circuit that is:

I can not get the same current in the other branch as shown in the picture.

Could you please help me to solve this problem?

Note: the dimensions of W and L for the transistors are shown and I selected them based on trial and error to get these results. Is there any rule to follow to select the best transistor dimensions?

Regards.