palermo

Newbie level 6

Dear community,

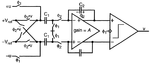

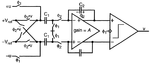

I have designed a 1st order 1-bit delta-sigma modulator. I have implemented the fully differential architecture proposed on p31 of Schreier's "Understanding Delta-Sigma Data Converters" book. After running the simulation in Cadence, I import the data into Matlab to process it.

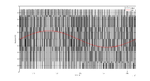

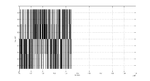

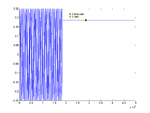

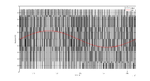

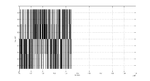

So as to have a high resolution fft, I want to run a simulation for 200 periods of input signal. However, resulting output signal is very well for first ~100 period and then sticks to the rails.

Do you have any idea why this happens?

Enclosed are the output graphics.

Thanks in advance!

I have designed a 1st order 1-bit delta-sigma modulator. I have implemented the fully differential architecture proposed on p31 of Schreier's "Understanding Delta-Sigma Data Converters" book. After running the simulation in Cadence, I import the data into Matlab to process it.

So as to have a high resolution fft, I want to run a simulation for 200 periods of input signal. However, resulting output signal is very well for first ~100 period and then sticks to the rails.

Do you have any idea why this happens?

Enclosed are the output graphics.

Thanks in advance!