melkord

Full Member level 3

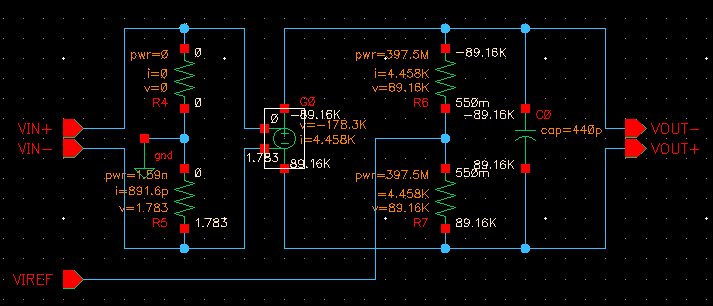

I have tried to change the gmin to a smaller value and try to check the gmin-check option. the problem is still there.

This ideal amp instance is used also in another circuit and the simulation works ok.

The problematic nodes drive the Gate of MOSFETs.

What simulation option I have to check to solve this issue?

This ideal amp instance is used also in another circuit and the simulation works ok.

The problematic nodes drive the Gate of MOSFETs.

What simulation option I have to check to solve this issue?

Code:

Opening the PSF file ../psf/dc.dc ...

Important parameter values:

reltol = 100e-06

abstol(V) = 1 uV

abstol(I) = 1 pA

temp = 27 C

tnom = 27 C

tempeffects = all

gmindc = 1 pS

Trying `homotopy = gmin'.

Notice from spectre at Vtgc = 1.8 during DC analysis `dc'.

GminDC = 1 pS is large enough to noticeably affect the DC solution.

dV(I13.I53.M2.m1:int_d) = -34.6437 mV

Use the `gmin_check' option to eliminate or expand this report.

Bad pivoting is found during DC analysis. Option dc_pivot_check=yes is recommended for possible improvement of convergence.

Warning from spectre at Vtgc = 1.8 during DC analysis `dc'.

WARNING (CMI-2375): M17.m1: Vgs has exceeded the oxide breakdown voltage of `vbox' = 11.7 V.

WARNING (CMI-2377): M17.m1: Vgd has exceeded the oxide breakdown voltage of `vbox' = 11.7 V.

WARNING (CMI-2375): M18.m1: Vgs has exceeded the oxide breakdown voltage of `vbox' = 11.7 V.

WARNING (CMI-2377): M18.m1: Vgd has exceeded the oxide breakdown voltage of `vbox' = 11.7 V.

Notice from spectre at Vtgc = 1.79 during DC analysis `dc'.

GminDC = 1 pS is large enough to noticeably affect the DC solution.

dV(I13.I53.M2.m1:int_d) = -34.6435 mV

Use the `gmin_check' option to eliminate or expand this report.

Bad pivoting is found during DC analysis. Option dc_pivot_check=yes is recommended for possible improvement of convergence.