AllenD

Member level 5

Hi Team

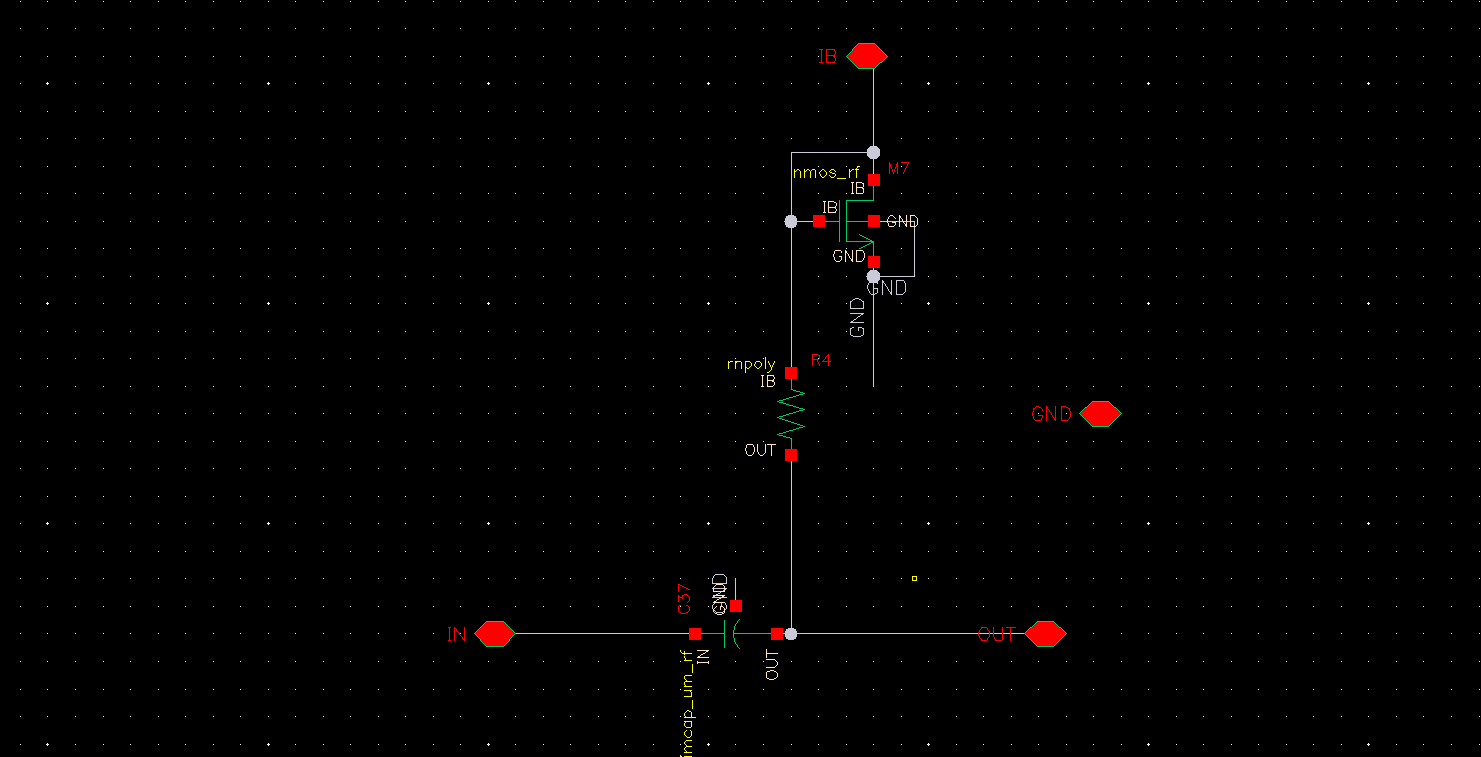

I am trying to design a DC blocking cap to only couple my AC signal from the first stage to the second stage of my amplifier.

Can I ask a few questions? I am thinking using the most simple RC topology with a diode connected NMOS to supply the DC voltage, as in the picture.

Assuming the frequency of my coupled AC signal is 1GHz, I know I want the C to be large enough as an AC short and the R large enough to offer a DC voltage at the OUT terminal but not interfere the AC signal at the OUT terminal. But Can you please tell me how should I choose the minimum R and C values? Is there any rule of thumbs to go?

Also, regarding the layout. The C I can use is from M5 and above. and R I can use is R-poly. For a relative big RC, both of them are consuming a lot of die space. Is it a good practice to layout them overlapping? And since there is no trace from M1 to M4 (R is on poly layer and C is M5 and above), should I route some signal traces in between?

Thanks

Al

I am trying to design a DC blocking cap to only couple my AC signal from the first stage to the second stage of my amplifier.

Can I ask a few questions? I am thinking using the most simple RC topology with a diode connected NMOS to supply the DC voltage, as in the picture.

Assuming the frequency of my coupled AC signal is 1GHz, I know I want the C to be large enough as an AC short and the R large enough to offer a DC voltage at the OUT terminal but not interfere the AC signal at the OUT terminal. But Can you please tell me how should I choose the minimum R and C values? Is there any rule of thumbs to go?

Also, regarding the layout. The C I can use is from M5 and above. and R I can use is R-poly. For a relative big RC, both of them are consuming a lot of die space. Is it a good practice to layout them overlapping? And since there is no trace from M1 to M4 (R is on poly layer and C is M5 and above), should I route some signal traces in between?

Thanks

Al