alftel

Member level 1

Hello guys (and gals),

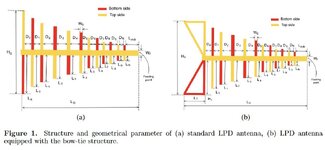

I wonder what it will take money wise to task any of you who owns or have an access to licensed CST and HFSS software to design, simulate/adjust Log Periodic Dipole Array (LPDA) antenna based on our specification, such as maximum size, Err and frequency range. We can provide a preliminary "good guess" measurements to start from. Teflon material, 1.52mm, rated to 10 GHz, 1oz ENIG finishing. Please ping me in private to alex@alftel.com

Cheers,

Alex

I wonder what it will take money wise to task any of you who owns or have an access to licensed CST and HFSS software to design, simulate/adjust Log Periodic Dipole Array (LPDA) antenna based on our specification, such as maximum size, Err and frequency range. We can provide a preliminary "good guess" measurements to start from. Teflon material, 1.52mm, rated to 10 GHz, 1oz ENIG finishing. Please ping me in private to alex@alftel.com

Cheers,

Alex