rakeshmglth

Newbie level 1

Dear all,

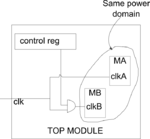

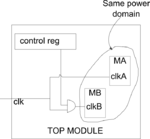

I am trying to perform clock gating for a submodule present in a bigger design. I want to disable/enable the clock to this submodule depending on a control register. The module I want to clock gate is MB as shown in the attached figure.

I implement this is verilog using and AND gate as shown and synthesize using Synopsys design compiler. Note that I do not want to use compile_ultra -gate_clock command as I do not want to clock gate any other modules in the whole design.

The problem arises when running with the sdf that I generate. The tool generates a huge delay for the ouput of the and gate as shown in the sdf snippet below.

(CELL

(CELLTYPE "CELL_FROM_LIB")

(INSTANCE interp_clk_gate_inst/U3)

(DELAY

(ABSOLUTE

(COND !B (IOPATH A Z (19412.504:19412.631:19412.631) (5637.378:5637.325:5637.325)))

(COND A (IOPATH B Z (19473.148:19473.148:19473.148) (5625.532:5625.532:5625.532)))

)

)

)

The constraints I am using are shown below.

Is there a specific way to tell the tool to buffer more if needed to fix this huge delay?

Thanks in advance.

Rakesh

I am trying to perform clock gating for a submodule present in a bigger design. I want to disable/enable the clock to this submodule depending on a control register. The module I want to clock gate is MB as shown in the attached figure.

I implement this is verilog using and AND gate as shown and synthesize using Synopsys design compiler. Note that I do not want to use compile_ultra -gate_clock command as I do not want to clock gate any other modules in the whole design.

The problem arises when running with the sdf that I generate. The tool generates a huge delay for the ouput of the and gate as shown in the sdf snippet below.

(CELL

(CELLTYPE "CELL_FROM_LIB")

(INSTANCE interp_clk_gate_inst/U3)

(DELAY

(ABSOLUTE

(COND !B (IOPATH A Z (19412.504:19412.631:19412.631) (5637.378:5637.325:5637.325)))

(COND A (IOPATH B Z (19473.148:19473.148:19473.148) (5625.532:5625.532:5625.532)))

)

)

)

The constraints I am using are shown below.

Code:

create_clock -period ${CLOCK_PERIOD} [get_ports clk]

set_drive 0 {clk}

#set_propagated_clock [all_clocks]

#add around 5% uncertainty

set_clock_uncertainty 0.4 clk

set_dont_touch_network {clk}

create_generated_clock -name interp_gated_clk -source [get_ports {clk}] -divide_by 1 [get_pins interp_clk_gate_inst/gclk]

update_timing

set_clock_gating_check -setup 0.15 -hold 0.03 interp_gated_clk

update_timing

set_propagated_clock interp_gated_clk

set_false_path -from [get_ports rst]Is there a specific way to tell the tool to buffer more if needed to fix this huge delay?

Thanks in advance.

Rakesh