newbie_hs

Full Member level 1

Dear Team,

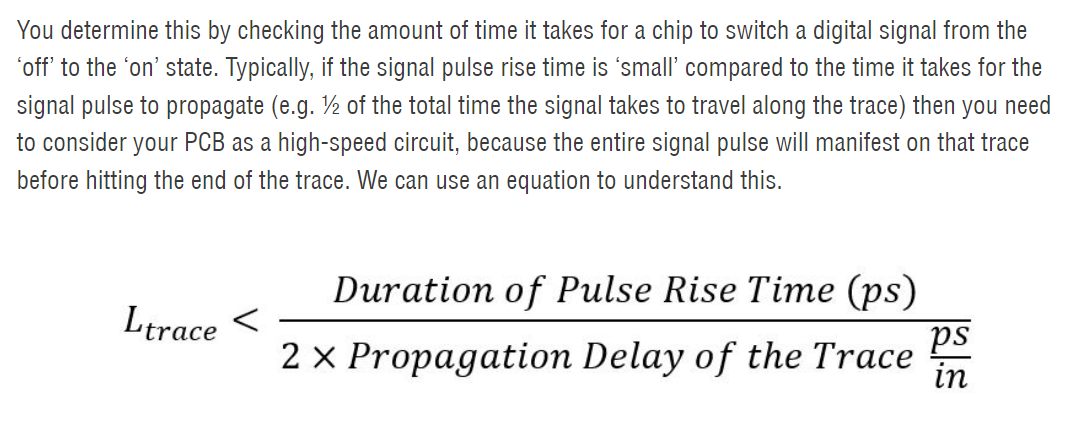

According to this link,we can consider a PCB trace as transmission line when,

I have see this explanation many places.But no one explains how transmission line effects comes when rise time is smaller than 2*times propagation delay

and how transmission line effect disappears when 2*times propagation delay is less than rise time.

Can someone please explain this.

According to this link,we can consider a PCB trace as transmission line when,

I have see this explanation many places.But no one explains how transmission line effects comes when rise time is smaller than 2*times propagation delay

and how transmission line effect disappears when 2*times propagation delay is less than rise time.

Can someone please explain this.