Cesar0182

Member level 5

Greetings, tell you that a couple of days ago I am migrating a project for a Virtex-5 made in ISE 14.5 to Kintex Ultrascale in Vivado 2019.2. At the moment I have managed to update and adapt almost all the ip cores with the exception of Aurora 8B10B since I cannot generate the same size of the tkeep signal that the previous version has. Could someone tell me how I can configure this to get a 3-bit tkeep?

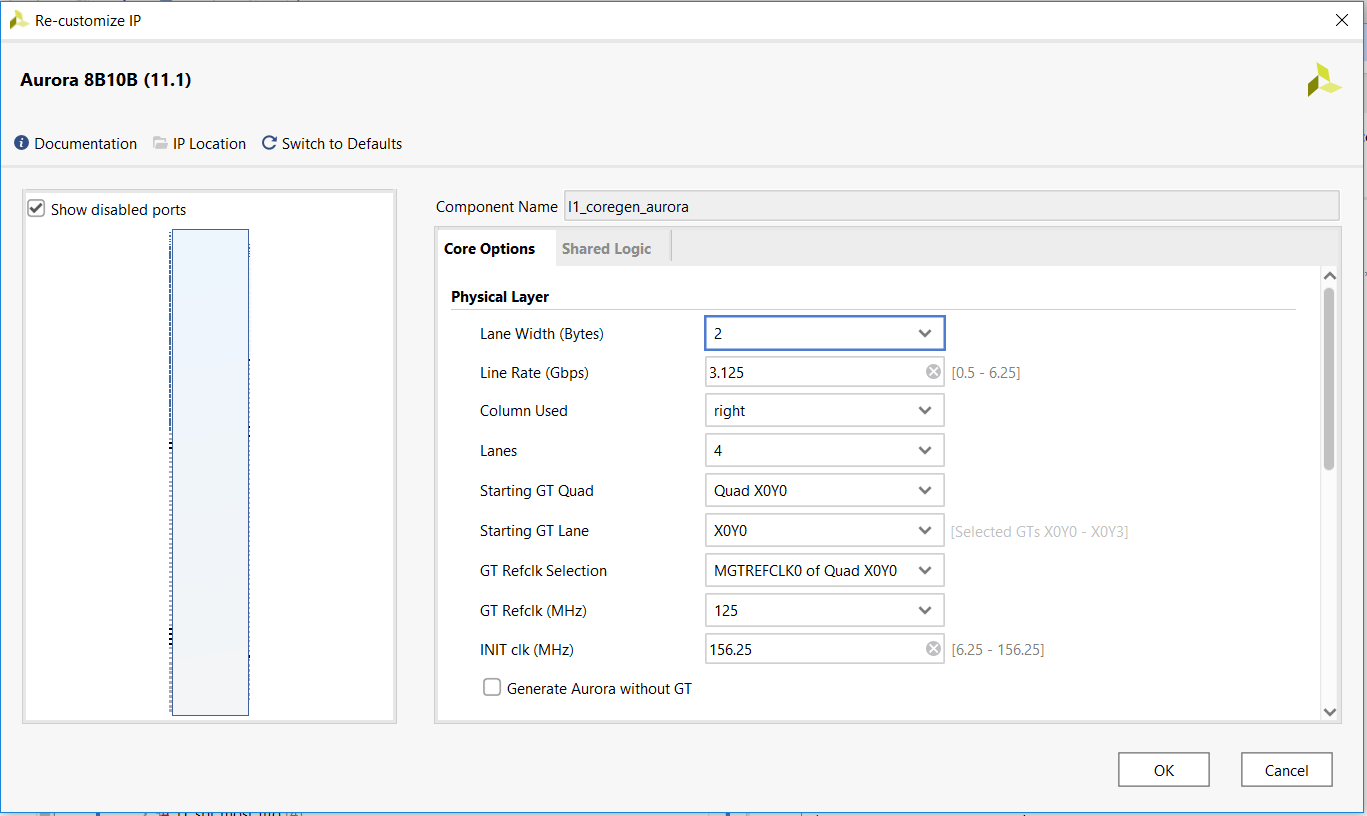

this is the configuration in Vivado, this generates a tkeep = 8 bits

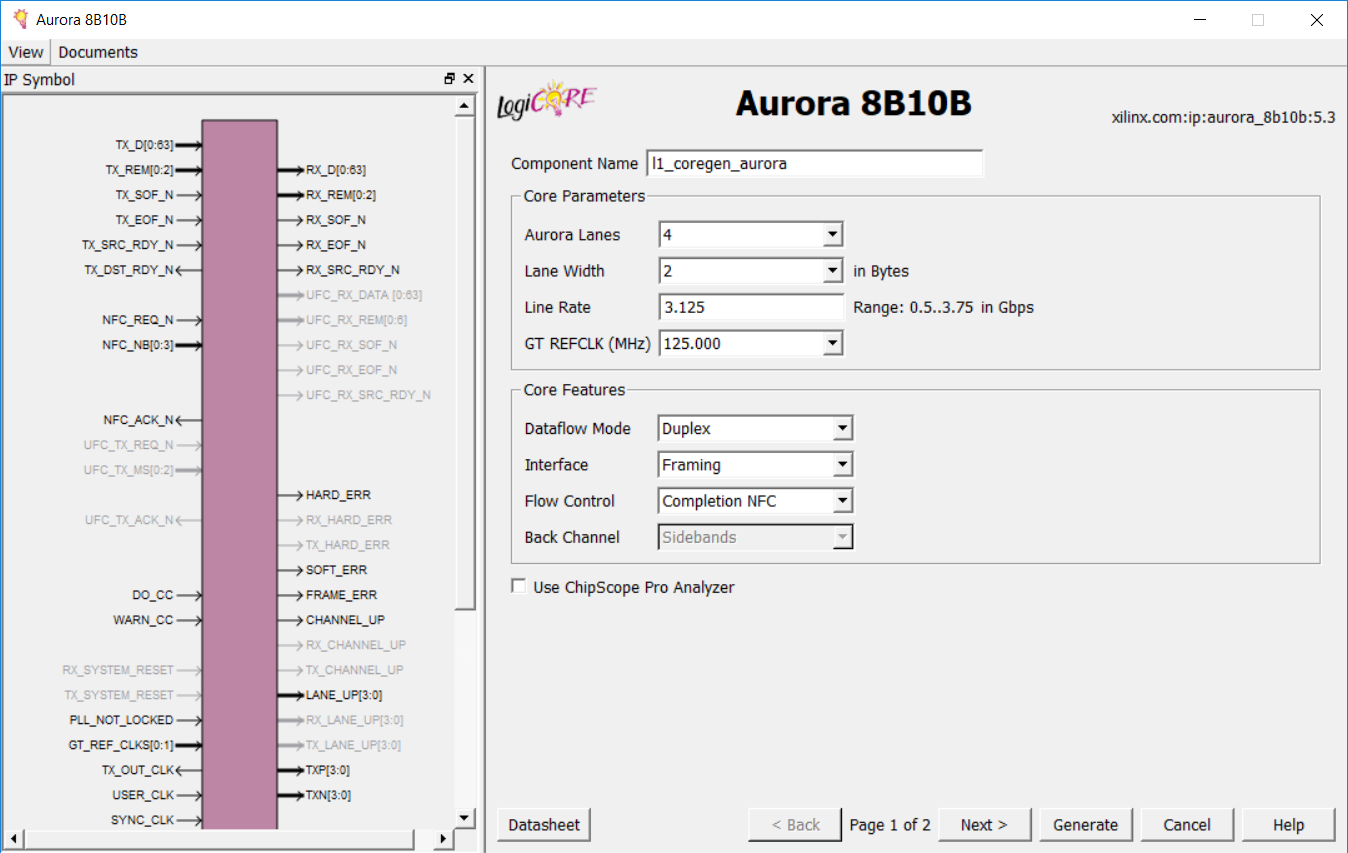

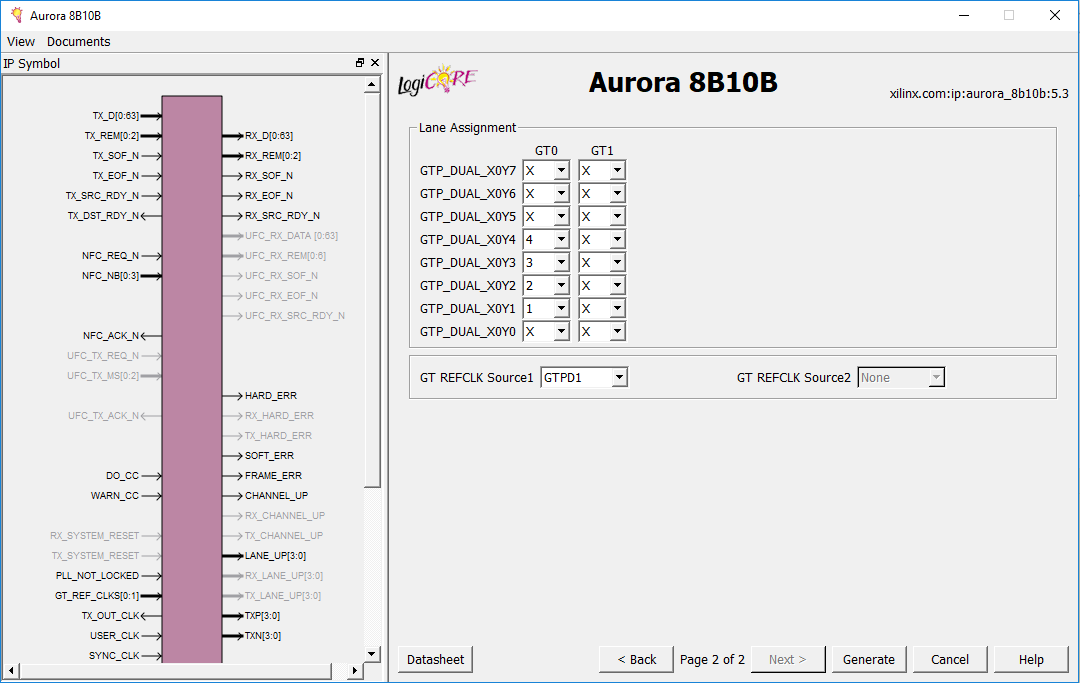

this is the configuration in ISE, this generates a tkeep = 3 bits

this is the configuration in Vivado, this generates a tkeep = 8 bits

this is the configuration in ISE, this generates a tkeep = 3 bits