Ashokb431

Junior Member level 1

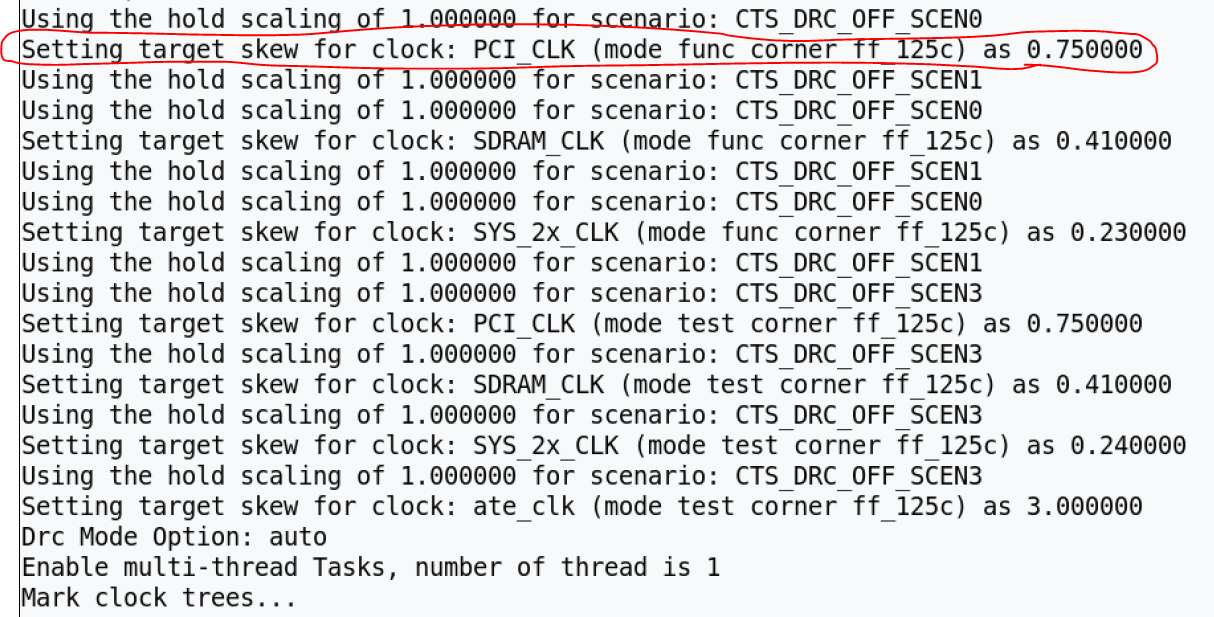

while I am running CTS (clock_opt -from build_clock -to build_clcok), in the log file i am getting like this.

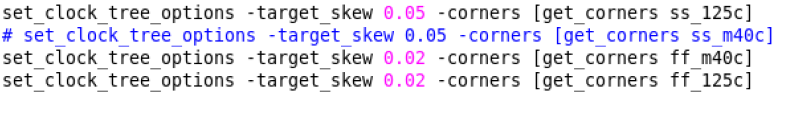

but those target skew values i already mentioned in the clock specification file with some other different values like this.

i.e., in log file i am getting target skew value as 0.75 for PCI_CLK in func mode and in ff_125c corner but in clock specification file which i already mentioned it as 0.02.

what is the reason for getting like this?

but those target skew values i already mentioned in the clock specification file with some other different values like this.

i.e., in log file i am getting target skew value as 0.75 for PCI_CLK in func mode and in ff_125c corner but in clock specification file which i already mentioned it as 0.02.

what is the reason for getting like this?