Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 262

Hi, I'm tring to simulate a simple design adder, but when simulation, the CLK signal stay 0 so that no wave for me debug. Can you help me?

My codes and script are shown as below,

Adder module:

testbench:

Makefile:

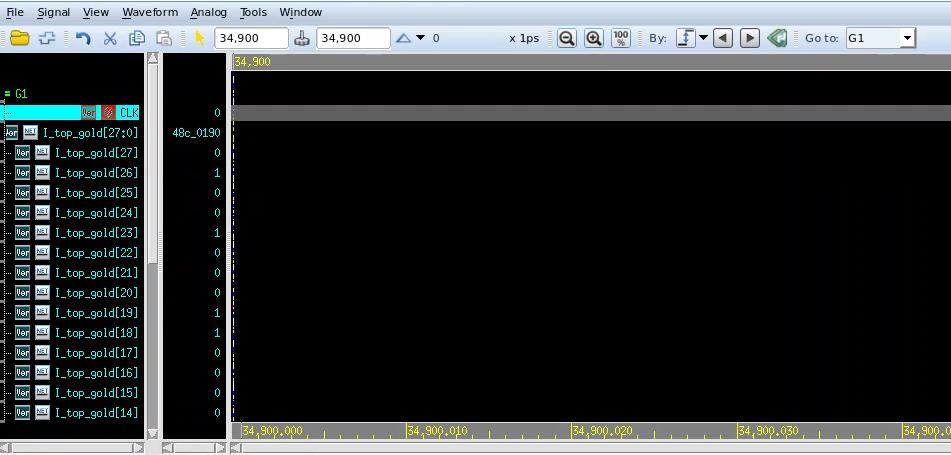

When i type ` make all , get into verdi, there no wave in CLK, i mean there is CLK signal, but it stays 0, like:

what should i do fo that?

My codes and script are shown as below,

Adder module:

Code:

module top(input wire clk, input wire [27:0] io_in, output wire [27:0] io_out, io_oeb);

wire rst = io_in[0];

reg [15:0] ctr;

always @(posedge clk)

if (rst)

ctr <= 0;

else

ctr <= ctr + 1'b1;

assign io_out = {10'h123, ctr, rst, 1'b0}; // pass thru reset for debugging

assign io_oeb = 28'b1;

endmoduletestbench:

Code:

module adder_tb;

reg [27:0] O_top = 0;

reg CLK;

wire [27:0] I_top_gold, oeb_gold, T_top_gold;

top dut_i (

.clk(CLK),

.io_out(I_top_gold),

.io_oeb(oeb_gold),

.io_in(O_top)

);

assign T_top_gold = ~oeb_gold;

//always #50 CLK = (CLK === 1'b0);

always #50 CLK = ~CLK ;

integer i;

reg have_errors = 1'b0;

initial begin

CLK = 0;

repeat (100) @(posedge CLK);

O_top = 28'b1; // reset

repeat (100) @(posedge CLK);

$display("in_in = 0x%X, gold = 0x%X, gold = 0x%X", O_top, I_top_gold, T_top_gold);

repeat (50) @(posedge CLK);

$display("in_in = 0x%X, gold = 0x%X, gold = 0x%X", O_top, I_top_gold, T_top_gold);

O_top = 28'b0;

$display("in_in = 0x%X, gold = 0x%X, gold = 0x%X", O_top, I_top_gold, T_top_gold);

for (i = 0; i < 100; i = i + 1) begin

@(negedge CLK);

$display("in_in = 0x%X, gold = 0x%X, gold = 0x%X", O_top, I_top_gold, T_top_gold);

end

$fsdbDumpfile("adder_tb.fsdb");

$fsdbDumpvars(0,adder_tb);

$fsdbDumpSVA();

$fsdbDumpMDA();

$vcdpluson;

$vcdplusmemon;

if (have_errors)

$fatal;

else

$finish;

end

endmodule

module clk_buf(input A, output X);

assign X = A;

endmoduleMakefile:

Code:

all:clean comp sim

OUTPUT = efpga_presim

PDK_Path = /opt/eda/PDK/....../tcbn28hpcplusbwp30p140_110a

# -sverilog ${PDK_Path}/tcbn28hpcplusbwp30p140.v

comp:

vcs -R -full64 +v2k \

-timescale=1ps/1ps \

-sverilog +vcs+lic+wait -debug_access+all -kdb \

/verilog_codes/*.v \

+define+sdfannot+fsdb \

+neg_tchk \

-l com.log

sim:

./simv -l sim.log

# debug:

# dve -full64 -vpd vcdplus.vpd &

verdi:

verdi -f /verilog_codes/*.v \

-ssf adder_tb.fsdb -nolog

clean:

rm -rf csrc DVEfiles *.vpd simv simv* ucli.key vc_hdrs.h urg* *.log *.dump *profile*what should i do fo that?