AMSA84

Advanced Member level 2

- Joined

- Aug 24, 2010

- Messages

- 577

- Helped

- 8

- Reputation

- 16

- Reaction score

- 8

- Trophy points

- 1,298

- Location

- Iberian Peninsula

- Activity points

- 6,178

Hi guys,

I'd like to know if someone can give me a tip on how I can characterize a MOSFET switch.

I'd like to make some plots but I really don't know which one's I should focus, that is, for example:

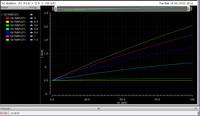

I though in plotting Vds VS Ids, Ids VS Vgs and think the Ron against what, Ids, Vgs? I though that those would be a good starting point but I don't know if I am thinking well.

The most important parameter here is the Ron but I would like to know how the MOSFET would behave with different values of Vgs and or Ids. Regarding the Vds, this Vds is the voltage across the transistor when in ON position. How can I predict the voltage here to make the simulation and with that get the Ron?

I am using Cadence & Spectre.

Regards.

I'd like to know if someone can give me a tip on how I can characterize a MOSFET switch.

I'd like to make some plots but I really don't know which one's I should focus, that is, for example:

I though in plotting Vds VS Ids, Ids VS Vgs and think the Ron against what, Ids, Vgs? I though that those would be a good starting point but I don't know if I am thinking well.

The most important parameter here is the Ron but I would like to know how the MOSFET would behave with different values of Vgs and or Ids. Regarding the Vds, this Vds is the voltage across the transistor when in ON position. How can I predict the voltage here to make the simulation and with that get the Ron?

I am using Cadence & Spectre.

Regards.