_Stavros_

Newbie

I'm a verilog beginner, I'm try to write a 24(29)-bit hexadecimal BCD counter. Can anyone explain how to implement it ?

Thanks !

Her is my code, but I'm need to check.

Who can help me ?

``

Code:

Thanks !

Her is my code, but I'm need to check.

Who can help me ?

``

Code:

Code:

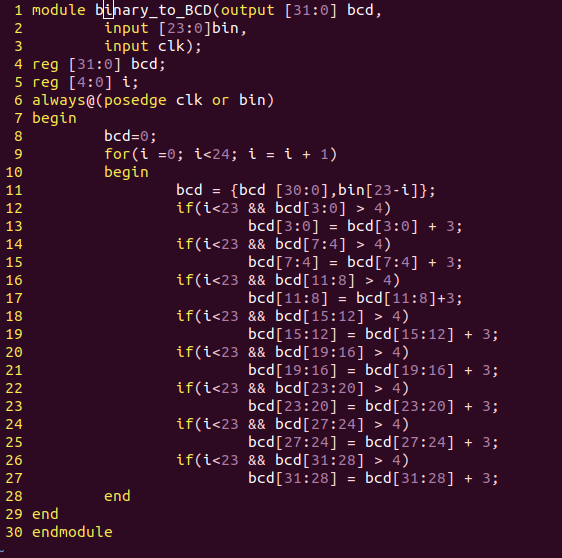

module binary_to_BCD(output [31:0] bcd,

input [23:0]bin,

input clk);

reg [31:0] bcd;

reg [4:0] i;

always@(posedge clk or bin)

begin

bcd=0;

for(i =0; i<24; i = i + 1)

begin

bcd = {bcd [30:0],bin[23-i]};

if(i<23 && bcd[3:0] > 4)

bcd[3:0] = bcd[3:0] + 3;

if(i<23 && bcd[7:4] > 4)

bcd[7:4] = bcd[7:4] + 3;

if(i<23 && bcd[11:8] > 4)

bcd[11:8] = bcd[11:8]+3;

if(i<23 && bcd[15:12] > 4)

bcd[15:12] = bcd[15:12] + 3;

if(i<23 && bcd[19:16] > 4)

bcd[19:16] = bcd[19:16] + 3;

if(i<23 && bcd[23:20] > 4)

bcd[23:20] = bcd[23:20] + 3;

if(i<23 && bcd[27:24] > 4)

bcd[27:24] = bcd[27:24] + 3;

if(i<23 && bcd[31:28] > 4)

bcd[31:28] = bcd[31:28] + 3;

end

end

endmodule

Last edited by a moderator: